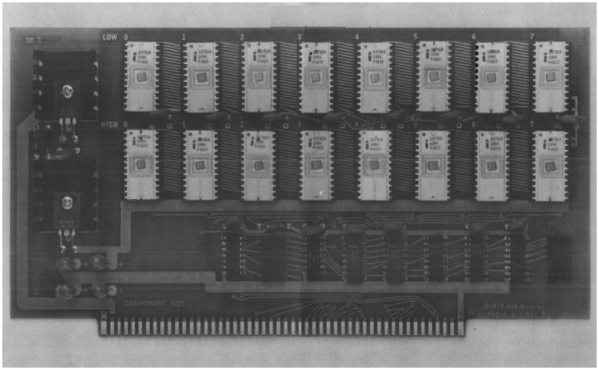

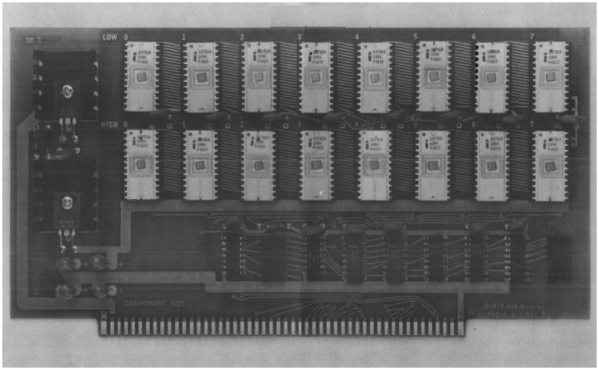

IMSAI - PROM 4 Board

This was an early S-100 EPROM card

taking only 1702's. I cannot locate a good color image. If anybody has one

I will place it here.

The PROM-4 board provides up to 4K of

addressable Read-Only-Memory, utilizing the Intel 3702-1702 PROM devices. The

board contained 256 bytes of memory for each 8702-1702 chip installed. Address

lines A0 through A7 are run directly to all PROM positions to select one of the

256 internal byte positions, while address lines A8 through A11 were used to

select and enable one particular PROM position through 8205 decoders. Address

lines A12 through A15 were jumper-selected to determine the board's enabling

address. The board was enabled when the 74LS30 NAND gate (C1 in schematic in

manual) inputs are all high, namely when the selected address appears on the

address bus, and the status line SMEMR is high. The Processor Ready line is

controlled by a 74195 shift register via an 8T97. The 74195 provided a

user-selected memory read delay, selectable with jumpers in the delay select

socket. The 74195 shift register is reset on the rising edge of the inverted

Board Enable (BDENA) signal. When addressed and enabled, an 8702-170Z PROM puts

out its data on the DO through D7 lines. The data output lines of all PROMS are

tied to these lines, and these lines are buffered via 8T97 sections to the DI0

through DI7 back plane bus lines. Power for the card logic is provided by a +5

volt regulator and a -5 volt regulator and a -4 volt Zener diode combination to

yield +5 and -9 volts.

The manual for this board can be

obtained here.

Other IMSAI S-100 Boards

4KRAM

8080CPU

EPROM-Programmer

MPU-B

PIC-8 PIO

PROM-4 SIO

VIO

MIO

FDC (FIB/FIM)

This page was last modified

on

01/08/2011