# CHAPTER 7 APPENDIX

| 7.1  | Main CPU (Z80)                                           | 7- 1 |

|------|----------------------------------------------------------|------|

| 7.2  | Slave CPU 6303                                           | 7- 6 |

| 7.3  | Sub-CPU 7508                                             | 7- 9 |

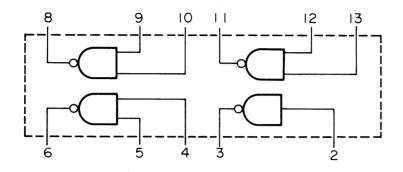

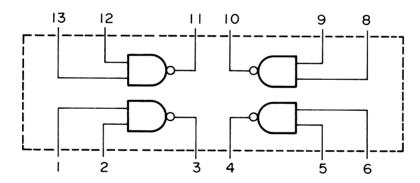

| 7.4  | Gate Array GAH40D                                        | 7-12 |

| 7.5  | Gate Array GAH40M                                        | 7-17 |

| 7.6  | Gate Array GAH40S                                        | 7-29 |

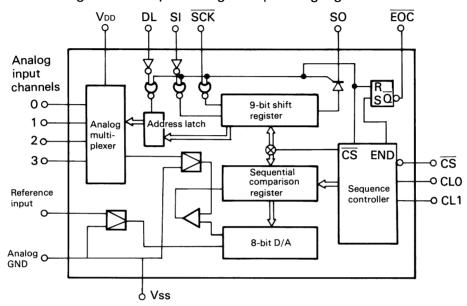

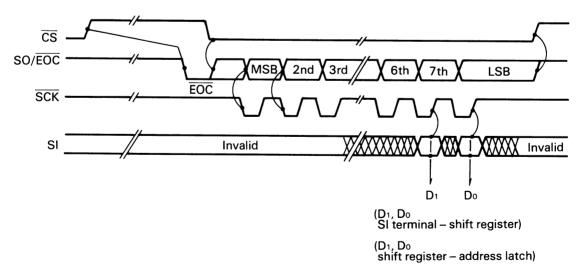

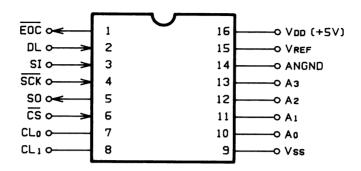

| 7.7  | A-D Converter μPD7001                                    | 7-34 |

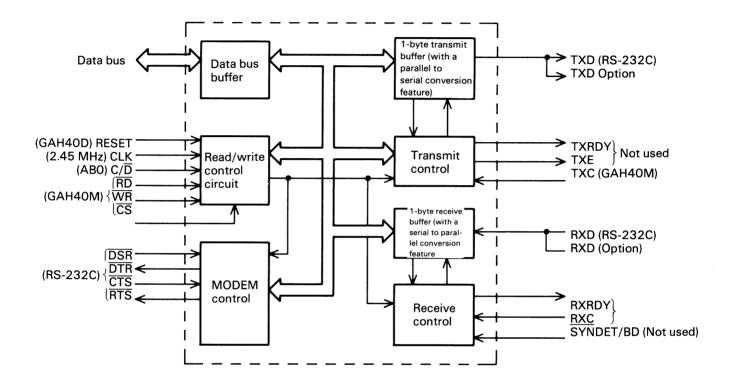

| 7.8  | Serial Controller 82C51                                  | 7-36 |

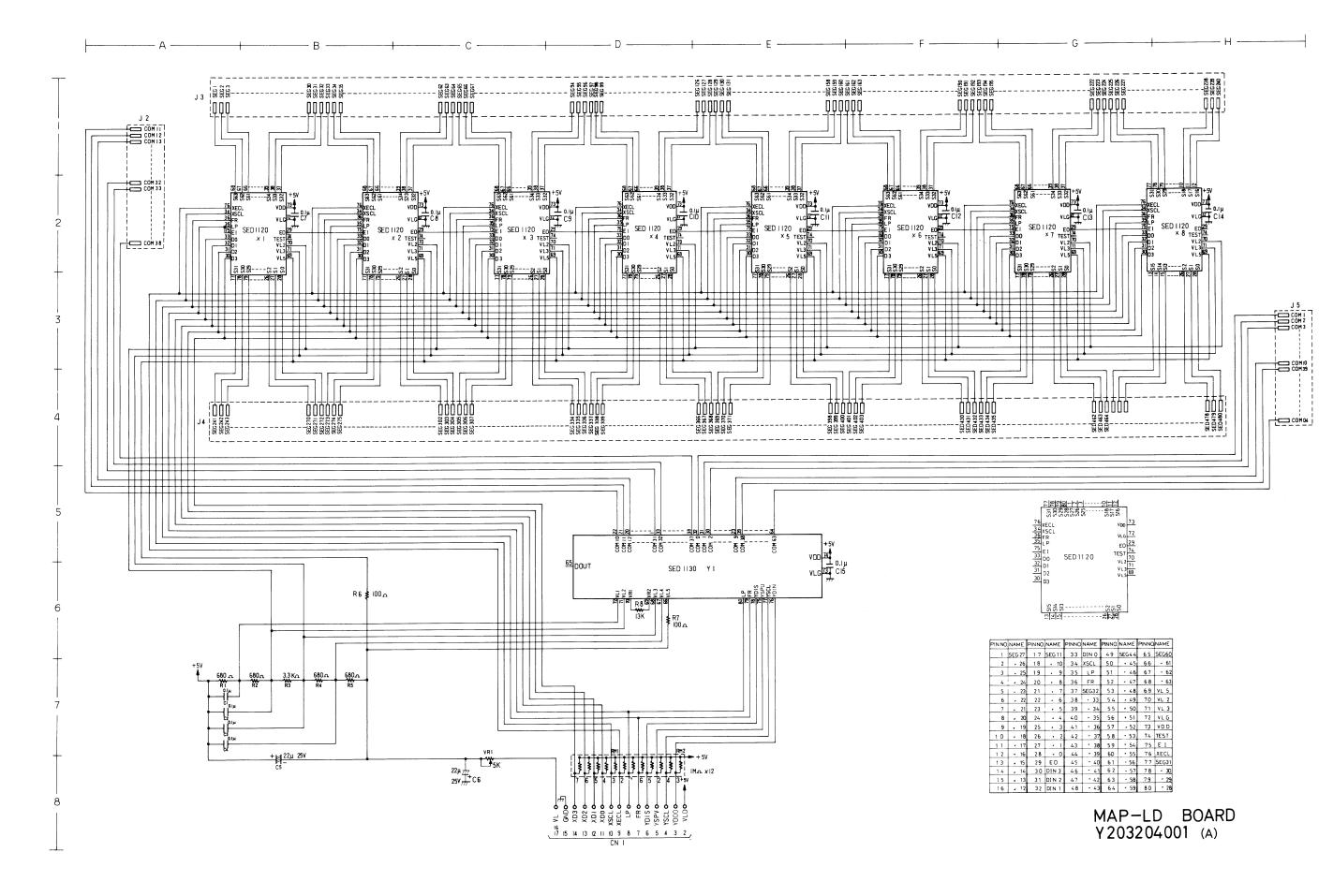

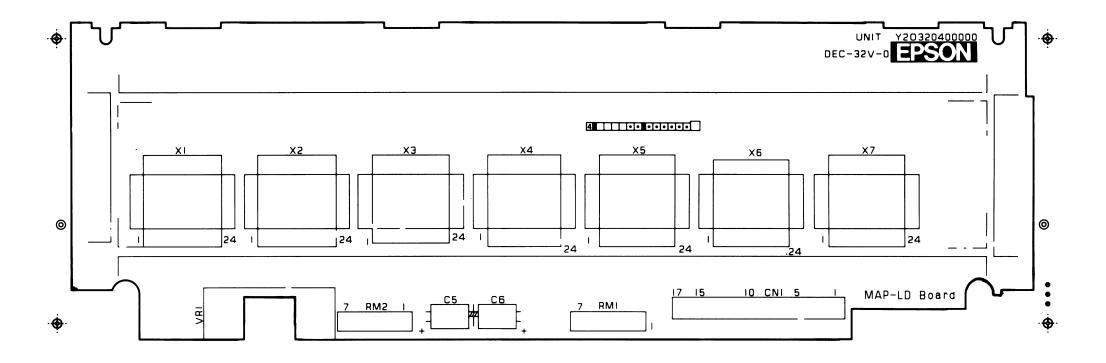

| 7.9  | SED1120 (LCD driver)                                     | 7-39 |

| 7.10 | SED1130 (LCD driver)                                     | 7-44 |

| 7.11 | LCD/V-RAM Controller SED1320                             | 7-50 |

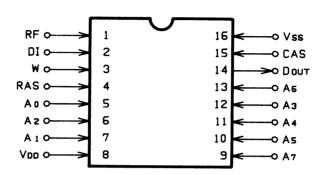

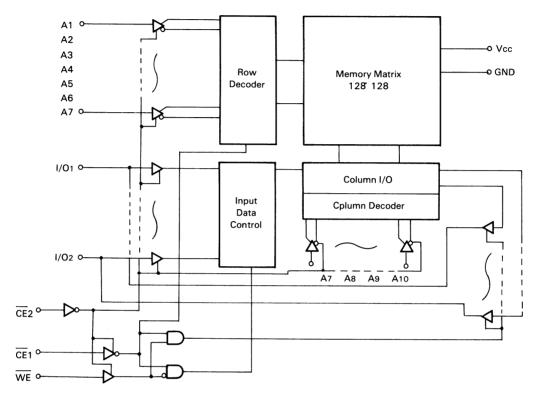

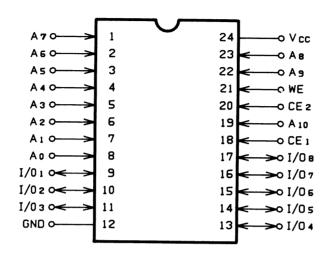

| 7.12 | D-RAM μPD4265                                            | 7-57 |

| 7.13 | V-RAM 6117                                               | 7-61 |

| 7.14 | Other ICs                                                | 7-64 |

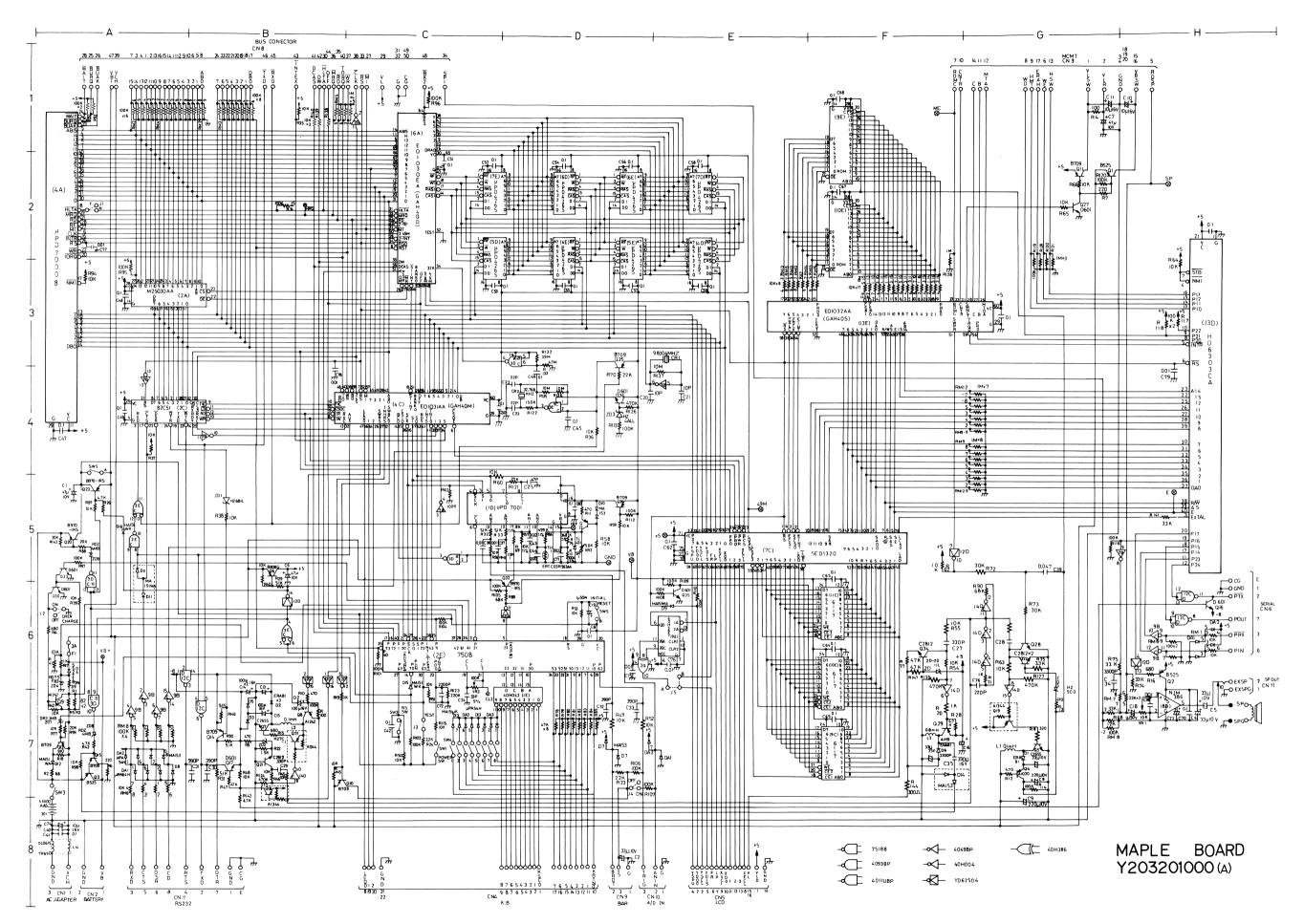

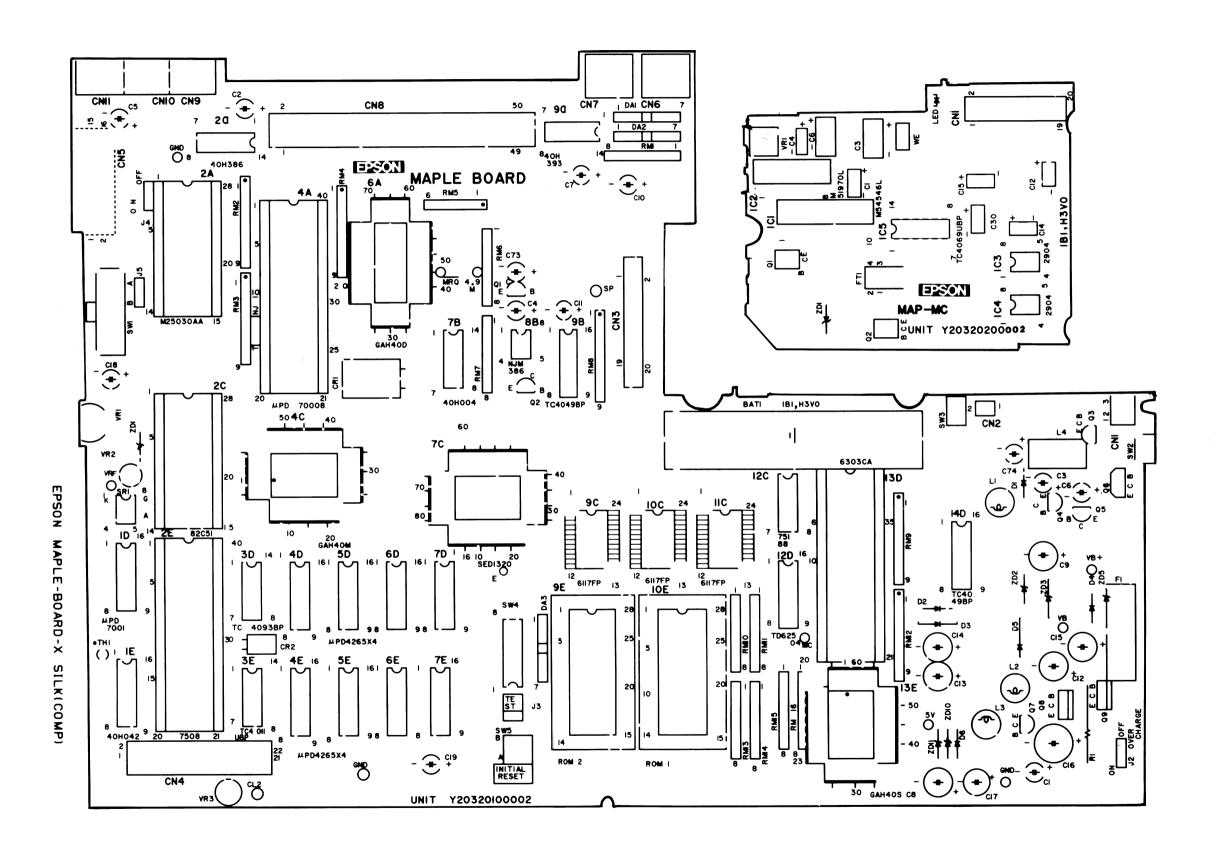

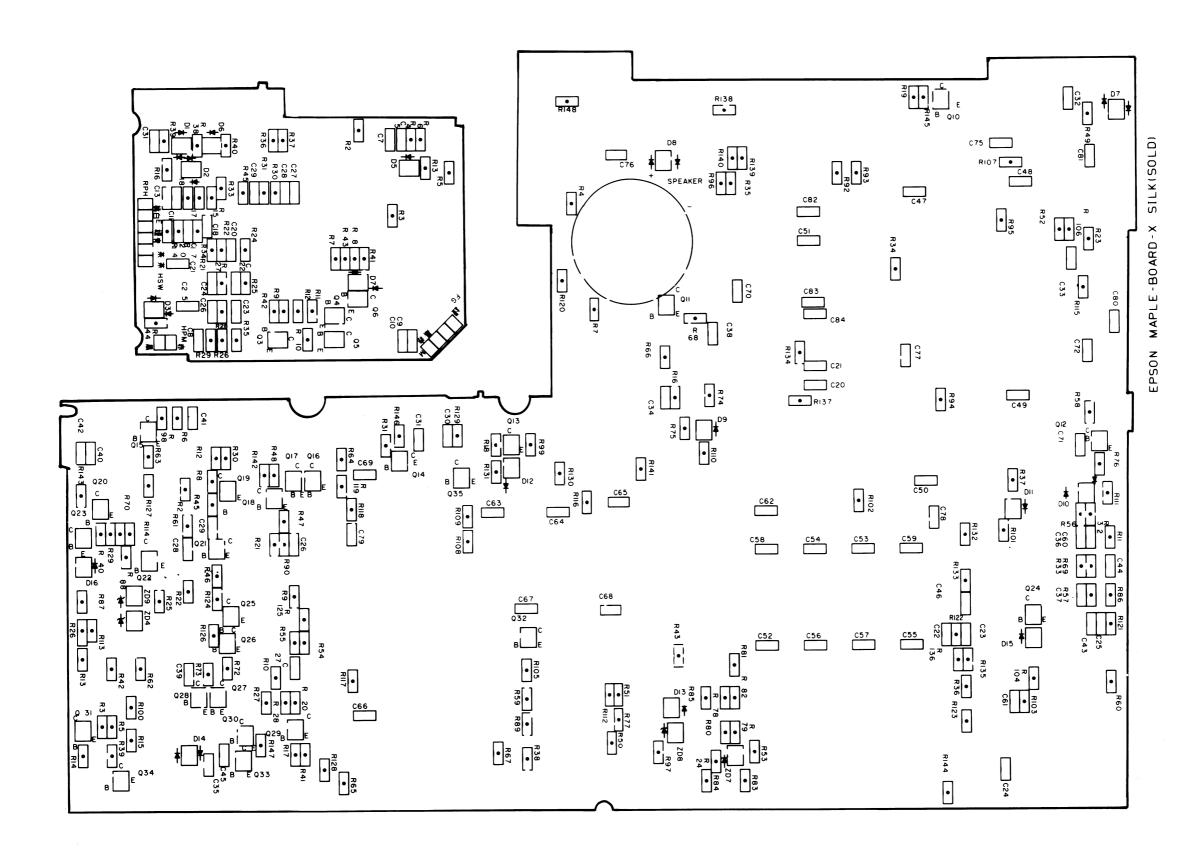

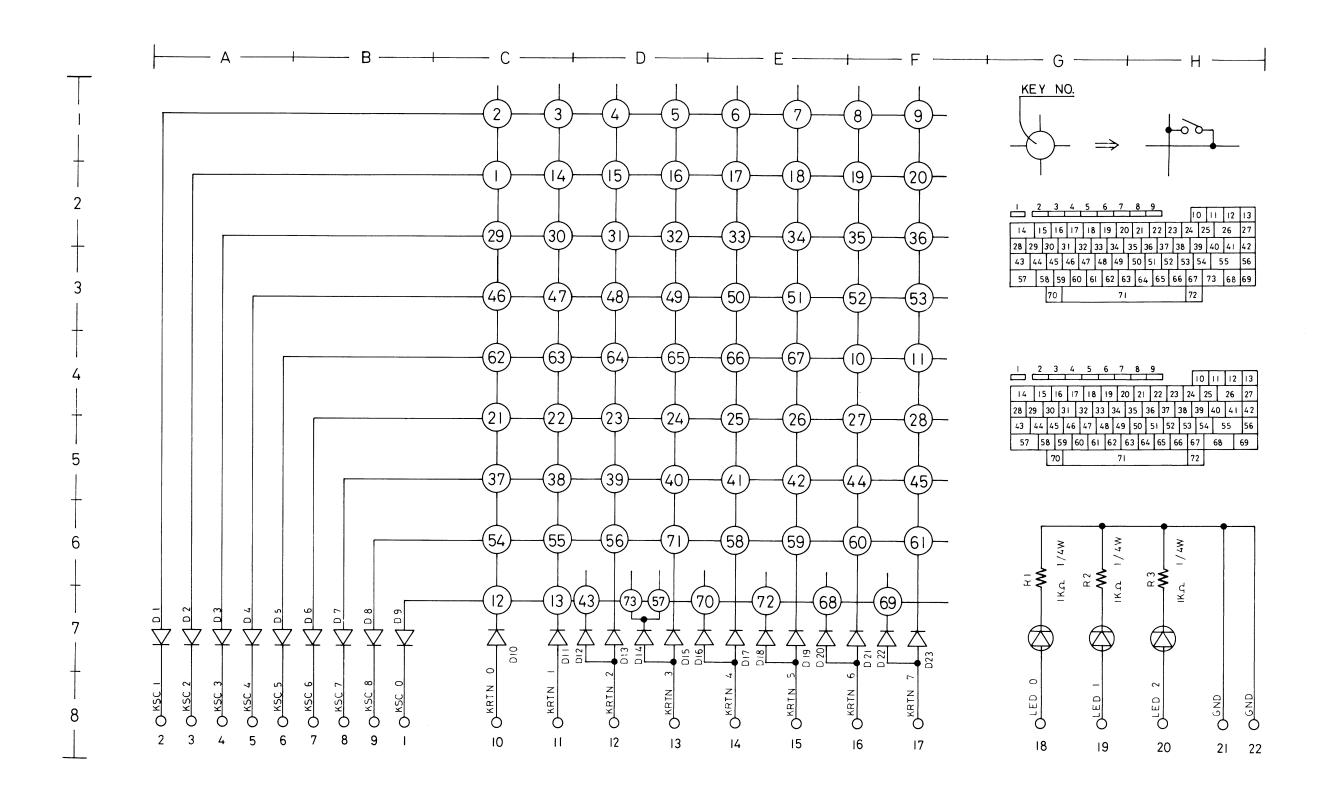

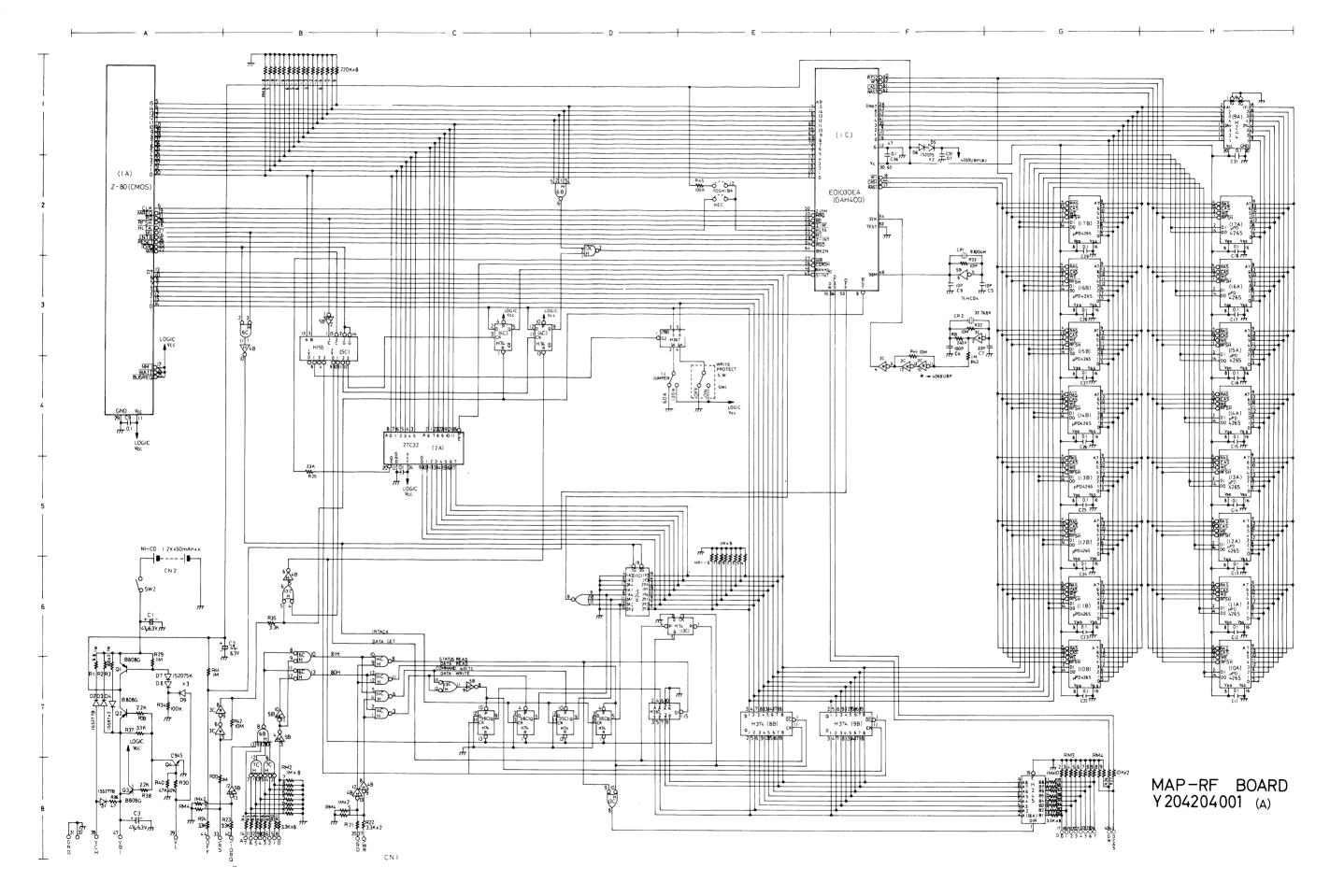

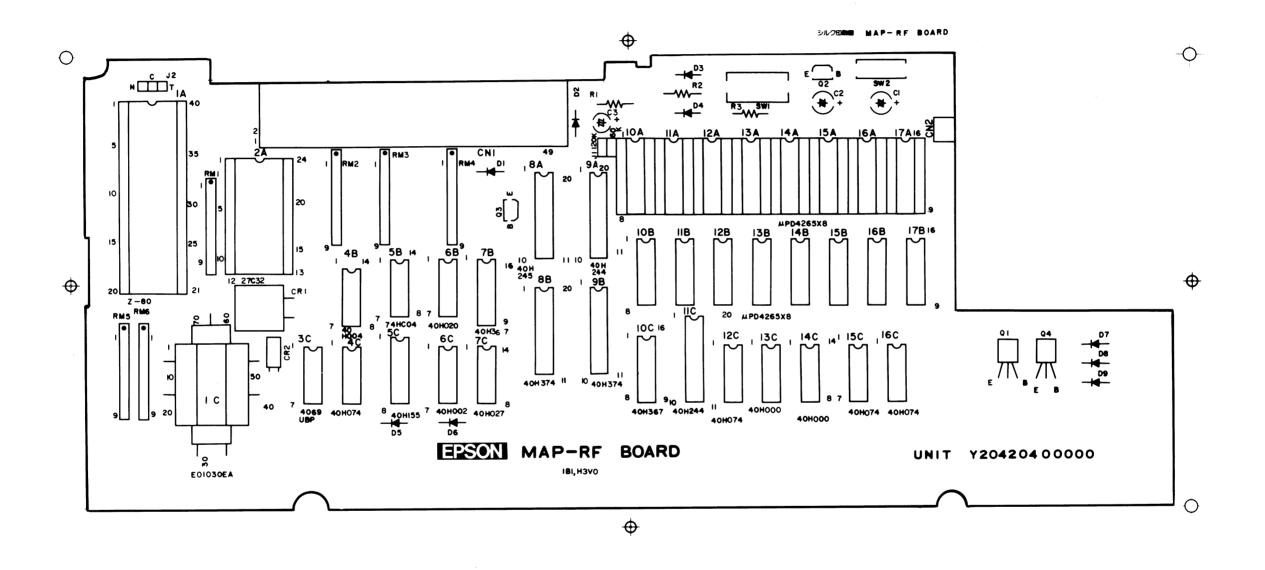

| 7.15 | Circuit Schematic Diagrams And Component Layout Diagrams | 7-67 |

# 7.1 Main CPU (Z80)

The main CPU is a CMOS-based, 8-bit microprocessor that controls the whole system. It directly controls DRAM, the RS-232C interface and the expansion interface (CN8), and sends and received commands and data both to and-from sub-CPUs 7508 and 6303 through the gate arrays.

Part No. X400260000 is currently used for the main CPU; however, jumper J1 has been incorperared on the MAPLE board so that in the future, other CPUs, which will expand the systems capabilities, can also be used.

#### 7.1.1 Operation

The main CPU operates at a clock rate of 2.45 MHz, making the instruction cycle approximately  $1.6\mu s$ .

1 state :  $1/(2.45 \times 10^8) = 408 \mu s$

1 cycle :  $408 \times 4(4 \text{ states}) = \text{Approx. } 1.6 \mu\text{s}$

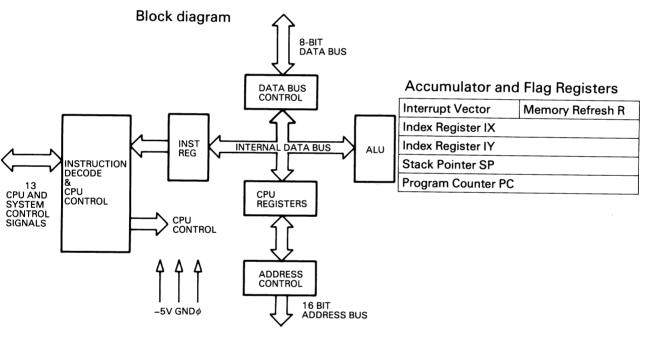

Fig. 7-1 shows a block diagram of the main CPU. Registers consist of general-purpose registers, accumulator registers, and flag registers.

Fig. 7-1

# 7.1.2 Functions of Major Registers

1. Program counter (PC): 16 bits

Holds address of next instruction.

2. Stack pointer (SP): 16 bits

Holds address of the top of the stack memory in DRAM.

3. Index register (IX and IY): 16 bits

Used for index addressing.

4. Memory refresh register (R): 8 bits

Holds refresh address of DRAM. Lower seven bits are automatically incremented on execution of op code fetch cycle.

5. Interrupt page address register (I): 8 bits

Holds high-order 8 bits of the indirect address used for interrupt mode 2.

#### **7.1.3 Timing**

An instruction is normally executed in combination with one of the following three basic machine cycles:

- (1) Instruction op code fetch (MI cycle)

- (2) Memory read/write cycle

- (3) Input/output cycle

- \* The relation between clock, state and machine cycle is as follows.

- 1 state = 1 clock

- 1 machine cycle = 3 to 6 states

- 1 instruction cycle = 2 to 6 machine cycles

#### 7.1.4 Interrupt Function

The NMI (non maskable interrupt) line of the main CPU cannot be used because it is always pulled up by resistor R94. Therefore, only the maskable interrupt INTR line is valid in this machine. The interrupt function operates in one of the following three modes:

- Mode 0: Executes the instruction (normally RST or CALL) read in MI (mode condition after reset).

- Mode 1: Saves the content of the program counter and automatically causes a branch to 0038H.

- Mode 2: Executes an indirect CALL instruction according to the content of the index registor and the data which has been read.

- \* These interrupts may not be accepted when the BUAK signal is low. (I.C., that period when the CPU is keeping the bus open).

#### 70008 Main CPU

1. Location: MAPLE board, 4A

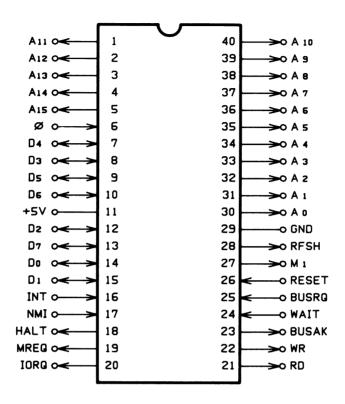

2. Pin Assignments

Table 7-1 70008 MAIN CPU Pin Assignments

| [             |                                    |                                              | CFO FIII Assignments                                                                                                                                                                |

|---------------|------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.       | Signal Name                        | In/Out                                       | Function                                                                                                                                                                            |

| -5<br>30-40   | ABO-15<br>(Address Bus)            | Tri-state output active high                 | A 16-bit address bus which outputs a memory address or I/O device number. It outputs the lower 7 bit D-RAM address for memory refresh.                                              |

| 7–10<br>12–15 | DB0-15<br>(Data Bus)               | Tri-state input<br>and output<br>active high | An 8-bit data bus which is used for data transfer between memory or an I/O device and main CPU.                                                                                     |

| 27            | M <sub>1</sub> (Machine Cycle one) | Output<br>active low                         | A signal which indicates that the starting machine cycle is the OP code fetch cycle.                                                                                                |

| 19            | MRQ<br>(Memory Request)            | Tri-state output:<br>active low              | A signal which indicates that the address information required for the memory read/write is output on the address bus. It is also output during memory refresh for synchronization. |

| Pin No. | Signal Name                       | In/Out                          | Function                                                                                                                                                                                                                                                                        |

|---------|-----------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20      | IORQ<br>(Input/Output<br>Request) | Tri-state output:<br>active low | During MI cycle Occurs when the CPU acknowledges a maskable interrupt, the external device to put the interrupt response vector on the data bus. Other than during MI cycle Indicates that the I/O device number required for this I/O read/write is output on the address bus. |

| 21      | RD<br>(Read)                      | Tri-state output:<br>active low | A signal which indicates that the data bus is in the input state. Memory or I/O device puts data on the data bus in synchronization with this signal.                                                                                                                           |

| 22      | WR<br>(Write)                     | Tri-state:<br>active low        | This signal indicates that the data bus is in the output state. The data to the I/O device or memory is put on the data bus in synchronization with this signal.                                                                                                                |

| 28      | RF<br>(Refresh)                   | Output:<br>active low           | This signal indicates, during MI cycle, that the dynamic RAM refresh address is output onto the lower seven bit lines of the address bus. Dynamic RAM reads the refresh address using the MREQ signal which is output together with the RFSH signal.                            |

| 18      | HALT<br>(Halt State)              | Output:<br>active low           | This signal indicates that CPU has HALTed as the result of a HALT instruction execution. The INT, NMI, or RESET signal is required to leave the HALT state.  CPU repeats dynamic RAM refresh by executing a NOP instruction, even while in the HALTed state.                    |

| 24      | WAIT<br>(Wait)                    | Input:<br>active low            | CPU remains in the WAIT state while this signal is active. A low speed memory or I/O device can be directly connected to CPU by using this signal.  No memory refresh is performed during the WAIT state.                                                                       |

REV.-A

| Pin No. | Signal Name                        | In/Out                            | Function                                                                                                                                                                                                                                                                                                        |

|---------|------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16      | INTR<br>(Interrupt Request)        | Input:<br>active low              | An interrupt request signal. When this signal becomes active, CPU enters the interrupt processing program after the current instruction has been executed.                                                                                                                                                      |

| 17      | NMI<br>(Non Maskable<br>Interrupt) | Input-negative:<br>edge triggered | A non-maskable interrupt request signal.  When this signal becomes active, CPU jumps to address 0066(16) after the current instruction has been executed, regardless of whether interrupt is enabled or not.  The NMI signal has a priority over the INT signal.                                                |

| 26      | RS<br>(Reset)                      | Input:<br>active low              | Resets CPU when active.                                                                                                                                                                                                                                                                                         |

| 25      | BURQ<br>(Bus Request)              | Input:<br>active low              | When active, this signal causes CPU to force the address bus (A <sub>0-15</sub> ), data bus (D <sub>0-7</sub> ), and tristate system control terminals (MREQ, IORQ, RD, and WD) in the high impedance state, freeing the external buses for another device.  The BUSRQ signal has priority over the NMI signal. |

| 23      | BUAK<br>(Bus<br>Acknowledge)       | Output:<br>active low             | When active, this signal indicates that CPU has forced the address bus, data bus, and tristate system control terminals in the high impedance state.                                                                                                                                                            |

| 6       | CLK<br>(Clock)                     | Input                             | A 0/+5V single-phase clock signal                                                                                                                                                                                                                                                                               |

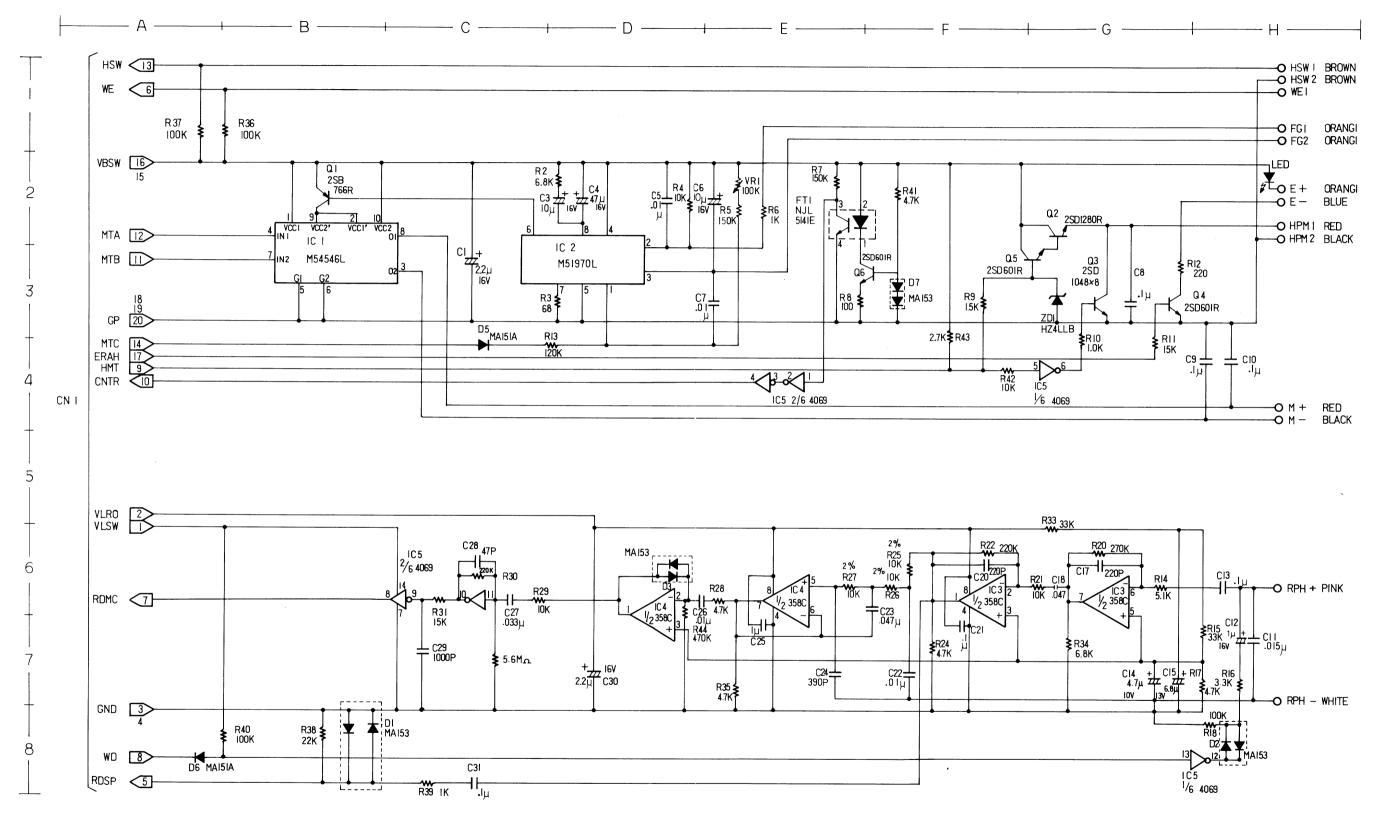

# 7.2 Slave CPU 6303

6303 is a 6800-series, 8-bit, C-MOS CPU. It incorporates a 4kB masked ROM which contains programs for controlling the microcassette tape drive, ROM capsule, V-RAM, LCD display unit, serial interface, and speaker. A mode six (Multiplexer Partial/Decode) is selected for the control operations. Stand-by and sleep modes, unique to 6303, are not used.

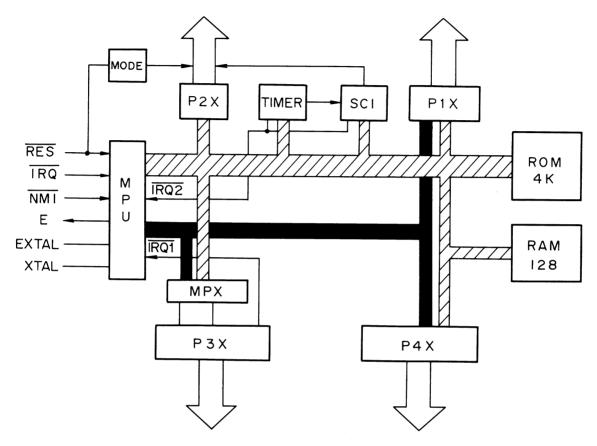

Fig. 7-2 6303 Slave CPU Functional Block Diagram

This computer uses a crystal oscillator for a 2.4576 MHz clock signal. The slave CPU operates with the 614.4 kHz system clock signal which is internally quartered from the primary frequency of 2.4576 MHz. The table opposite shows the port assignment.

| Port                         | Assignment          |  |

|------------------------------|---------------------|--|

| Port 1 Parallel I/O terminal |                     |  |

| Port 2                       | Serial I/O terminal |  |

| Port 3 Address/data terminal |                     |  |

| Port 4 Address terminal      |                     |  |

Table 7-2

#### Slave CPU 6303

1. Location: MAPLE Board, 130

2. Pin Assignment

Table 7-3 6303 Slave CPU Pin Assignments

| Pin No. | Signal<br>Name | In/Out | Function                                                |

|---------|----------------|--------|---------------------------------------------------------|

| 1       | G              | _      | GND                                                     |

| 2       | X<br>TAL       | ln     | Unused – reserved for exter-<br>nal clock signal input. |

| 3       | EX<br>TAL      | ln     | External clock signal input<br>2.4576 MHz               |

| 4       | NMI            | In     | Unused – reserved for non-<br>maskable interrupt input. |

| 5       | INTR           | In     | Interrupt request                                       |

| 6       | RS             | In     | Reset signal                                            |

| 7       | STB            | In     | Unused – reserved for Stand-<br>by signal input.        |

| 8       | P20            | In     | Microcassette tape read data (RDMC)                     |

| 9       | P21            | Out    | Microcassette tape write data (WD)                      |

| 10      | P22            | In     | Unused – reserved for operation mode setting.           |

| 11      | P23            | In     | Serial interface receive data                           |

| 12      | P24            | Out    | Serial interface transmit data                          |

| 13      | P10            | Out    | Microcassette head pinch<br>motor ON/OFF (HMT)          |

|         | Signal |        |                                            |

|---------|--------|--------|--------------------------------------------|

| Pin No. | Name   | In/Out | Function                                   |

| 14      | P11    | Out    | Microcassette tape erase<br>(ERAH)         |

| 15      | P12    | ln     | Microcassette tape write enable (WE)       |

| 16      | P13    | ln     | Microcassette tape head load/unload switch |

| 17      | P14    | ln     | Serial interface PIN signal                |

| 18      | P15    | Out    | Serial interface POUT signal               |

| 19      | P16    | Out    | Speaker output                             |

| 20      | P16    | Out    | Speaker power on/off                       |

| 21      | VC     | ln     | +5V (Circuit voltage)                      |

| 22      | A15    | Out    | Address bus                                |

| 23      | A14    | Out    | Address bus                                |

| 24      | A13    | Out    | Address bus                                |

| 25      | A12    | Out    | Address bus                                |

| 26      | A11    | Out    | Address bus                                |

| 27      | A10    | Out    | Address bus                                |

| 28      | A9     | Out    | Address bus                                |

| 29      | A8     | Out    | Address bus                                |

| Pin No. | Signal<br>Name | In/Out    | Function         |

|---------|----------------|-----------|------------------|

| 30      | DA7            | In<br>Out | Data address bus |

| 31      | DA6            | In<br>Out | Data address bus |

| 32      | DA5            | In<br>Out | Data address bus |

| 33      | DA4            | In<br>Out | Data address bus |

| 34      | DA3            | In<br>Out | Data address bus |

| 35      | DA2            | In<br>Out | Data address bus |

| Pin No. | Signal<br>Name | In/Out    | Function         |

|---------|----------------|-----------|------------------|

| 36      | DA1            | In<br>Out | Data address bus |

| 37      | DAO            | In<br>Out | Data address bus |

| 38      | R/W            | Out       | Read/Write       |

| 39      | AS             | Out       | Address strobe   |

| 40      | Ε              | Out       | ENABLE           |

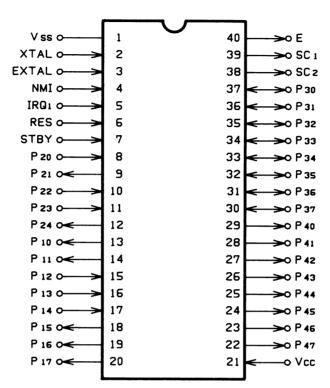

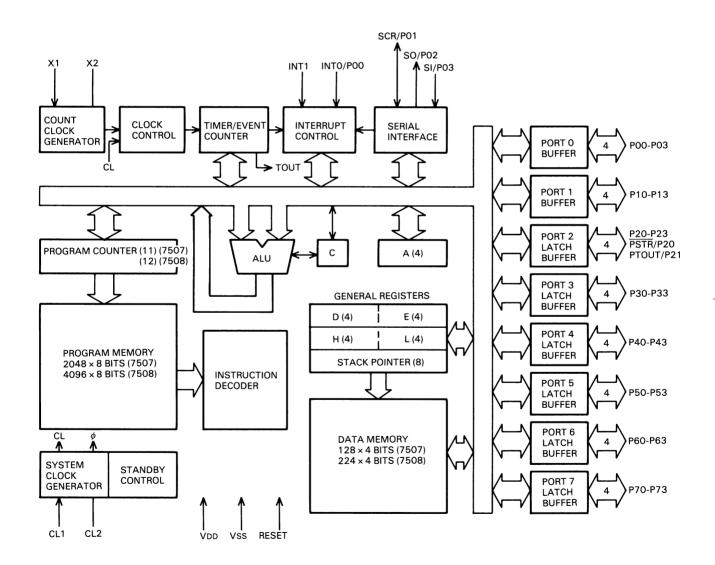

#### 7.3 Sub-CPU 7508

This is a 4-bit, C-MOS CPU which incorporates a masked ROM, timer, and serial interface, etc. This CPU is always backed up by the battery, regardless whether power is on or off, it provides the following control functions:

- 1. Power on/off (POWER switch and an associated program)

- 2. Keyboard scanning and auto-repeat

- 3. RESET switch

- 4. Temperature and battery voltage sensing

- 5. D-RAM refresh

- 6. Clock (calendar and alarm services)

The sub-CPU exchanges data with the main CPU in a bit-serial fashion via the gate array GAH40M. Fig. 7-3 is a functional block diagram of the sub-CPU. Table 7-4 lists the terminal signals and summarizes their functions.

Fig. 7-3

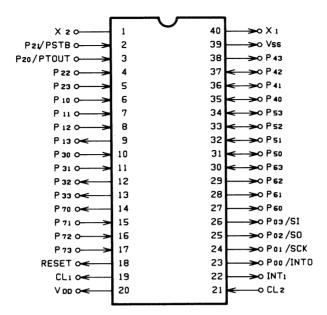

## 7508 (Sub-CPU)

1. Location: MAPLE Board, 2E

2. Pin Assignments

Table 7-4 7508 SUB-CPU Pin Assignments

| Pin No. | Signal Name | In/Out | Function                                                                                 |

|---------|-------------|--------|------------------------------------------------------------------------------------------|

| 1       | × 2         | In     | Unused.                                                                                  |

| 2       | P20         | Out    | GAH40M SIOR access control – H: 7508, L:<br>Main CPU                                     |

| 3       | P21         | Out    | A-D converter 7001 Chip Select - mode switching between address data and A-D conversion. |

| 4       | P22         | Out    | Ready signal                                                                             |

| 5       | P23         | Out    | A-D converter 7001 power on/off                                                          |

| 6       | P10         | In     | Key return 0                                                                             |

| 7       | P11         | In     | Key return 1                                                                             |

| 8       | P12         | ln     | Key return 2                                                                             |

| 9       | P13         | In     | Key return 3                                                                             |

| 10      | P30         | Out    | Key scan control                                                                         |

| 11      | P31         | Out    | Key scan control                                                                         |

| 12      | P32         | Out    | Key scan control                                                                         |

| 13      | P33         | Out    | Key scan control                                                                         |

| 14      | P70         | Out    | Power ON/OFF                                                                             |

| Pin No. | Signal Name | In/Out | Function                                                                        |

|---------|-------------|--------|---------------------------------------------------------------------------------|

| 15      | P71         | Out    | Data write – prevents FF latches in gate array at power off.                    |

| 16      | P72         | Out    | Data write – D-RAM refresh control signal during power off.                     |

| 17      | P73         | Out    | Data CAS                                                                        |

| 18      | RS          | In     | Reset signal input                                                              |

| 19      | CL1         | In     | Clock signal input                                                              |

| 20      | VC          | In     | +5V (Battery voltage: VB) terminal                                              |

| 22      | CL2         | ln     | Clock signal input                                                              |

| 23      | POO/INTO    | In     | POWER switch                                                                    |

| 24      | SCK         | Out    | Shift clock signal output – used for A-D conversion data/main CPU command read. |

| 25      | SO          | Out    | Serial data output                                                              |

| 26      | SI          | In     | Serial data output                                                              |

| 27      | P60         | In     | RESET switch                                                                    |

| 28      | P61         | In     | Charge start detection                                                          |

| 29      | P62         | In     | Analog interface trigger input                                                  |

| 30      | P63         | In     | Test point                                                                      |

| 31      | P50         | In     | Key return 4                                                                    |

| 32      | P51         | In     | Key return 5                                                                    |

| 33      | P52         | In     | Key return 6                                                                    |

| 34      | P53         | . In   | Key return 7                                                                    |

| 35      | P40         | Out    | Reset signal – initializes main CPU and slave CPU, etc. via GAH40.              |

| 36      | P41         | Out    | Charge mode control – normal/trickle charge.                                    |

| 37      | P42         | Out    | Auxiliary battery backup enable/disable control.                                |

| 38      | P43         | Out    | Interrupt to main CPU                                                           |

| 39      | G           | ln     | Ground terminal                                                                 |

| 40      | X1          | In     | External clock signal input – 1 kHz                                             |

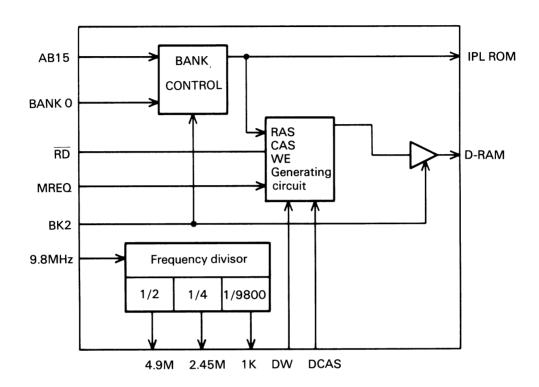

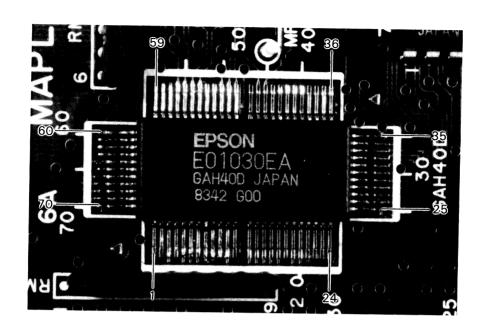

## 7.4 Gate Array GAH40D

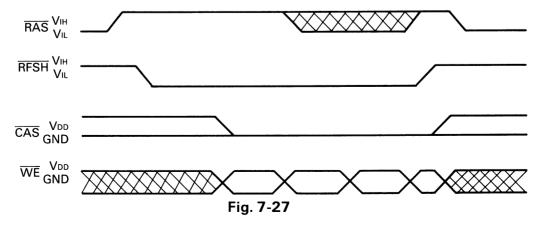

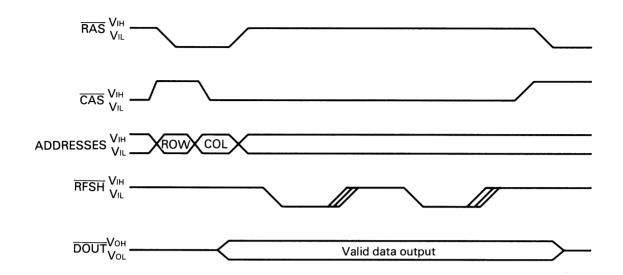

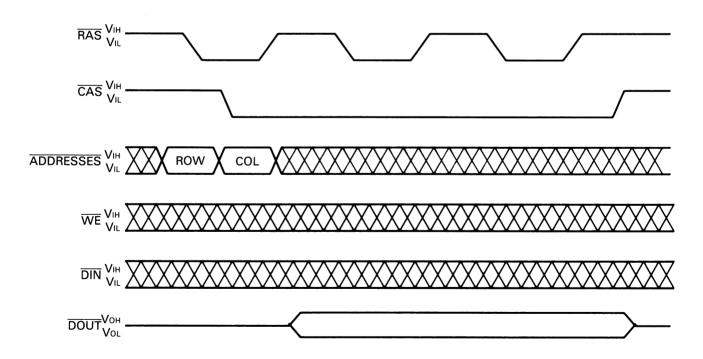

GAH40D is the gate array for D-RAM control. It controls memory access and memory refresh. It also incorporates a clock frequency divisor which divides 9.8 MHz input to 4.9 MHz, 2.45 MHz, 32 KHz and 1 KHz of clock frequency. Fig. 7-4 shows an internal block of diagram of the GAH40D.

Fig. 7-4

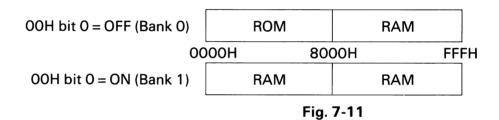

The BANK 0/1 signal is provided from the gate array GAH40M. The main CPU sends this signal by writing bit 0 to I/O address 00. (0: bank 0, 1: bank 1) BK2 signal is provided from the option unit.

## **GAH40D**

1. Location: MAPLE Board, 6A

2. Pin Assignment

Table 7-5 GAH40D Pin Assignments

| Pin No. | Signal Name | In/Out | Function                                                                                          |

|---------|-------------|--------|---------------------------------------------------------------------------------------------------|

| 1       | N/C         | -      | Not used.                                                                                         |

| 2       | N/C         | _      | Not used.                                                                                         |

| 3       | AB12        | In     | Address bus 12                                                                                    |

| 4       | N/C         | _      | Not used.                                                                                         |

| 5       | AB 6        | In     | Address bus 6                                                                                     |

| 6       | AB 13       | In     | Address bus 13                                                                                    |

| 7       | AB 5        | ln     | Address bus 5                                                                                     |

| 8       | RST         | In     | Reset input from sub-CPU 7508. Whole reset signal $\overline{RSQ}$ is generated from this signal. |

| 9       | DRA 2       | Out    | DRAM address 2 (10)                                                                               |

| 10      | DRA 1       | Out    | DRAM address 1 (9)                                                                                |

| 11      | AB 14       | ln     | Address bus 14                                                                                    |

| 12      | G           | _      | Ground                                                                                            |

| Pin No. | Signal Name | In/Out | Function                                                     |

|---------|-------------|--------|--------------------------------------------------------------|

| 13      | AB 4        | In     | Address bus 4                                                |

| 14      | AB 15       | In     | Address bus 15                                               |

| 15      | AB 3        | In     | Address bus 3                                                |

| 16      | DRA 0       | Out    | DRAM address 0(8)                                            |

| 17      | RAS1        | Out    | Low address stroke: RAS signal to RAS.                       |

| 18      | W1          | Out    | Write enable: WE signal to DRAM.                             |

| 19      | AB 2        | In     | Address bus 2                                                |

| 20      | AB 1        | In     | Address bus 1                                                |

| 21      | AB O        | In     | Address bus 0                                                |

| 22      | N/C         | _      | Not used                                                     |

| 23      | N/C         | _      | Not used                                                     |

| 24      | N/C         | _      | Not used                                                     |

| 25      | RD          | In     | Read signal                                                  |

| 26      | CSROM       | Out    | IPL ROM chip select signal                                   |

| 27      | MR          | Out    | Memory read signal                                           |

| 28      | Z-INT       | Out    | Interrupt request signal to main CPU                         |

| 29      | Z-RF        | In     | Refresh signal from main CPU                                 |

| 30      | VC          | _      | Circuit voltage (+5V)                                        |

| 31      | HLTA        | ln     | Halt signal                                                  |

| 32      | M1          | In     | Indicates that main CPU is in machine cycle 1 (opcode fetch) |

| 33      | MRQ         | In     | Memory request signal                                        |

| 34      | RSO         | Out    | System reset signal resets the whole machine.                |

| 35      | DRA 3       | Out    | DRAM address 3 (11)                                          |

| 36      | N/C         | _      | Not used                                                     |

| 37      | N/C         | _      | Not used                                                     |

| 38      | DRA 7       | Out    | DRAM address 7 (15)                                          |

| 39      | N/C         | _      | Not used                                                     |

| Pin No. | Signal Name | In/Out | Function                                                                                                                                                                        |

|---------|-------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40      | RF          | Out    | Refresh signal for DRAM                                                                                                                                                         |

| 41      | DRA 4       | Out    | DRAM address 4 (12)                                                                                                                                                             |

| 42      | DRA 5       | Out    | DRAM address 5 (13)                                                                                                                                                             |

| 43      | DRA 6       | Out    | DRAM address 6 (14)                                                                                                                                                             |

| 44      | CAS1        | Out    | Column address strobe: CAS signal to DRAM                                                                                                                                       |

| 45      | S-INT       | In     | Interrupt signal from gate array GAH40M.  Generates Z-INT signal and causes an interrupt to main CPU.                                                                           |

| 46      | BANK 1/0    | In     | Bank 0: Bank select signal from gate array GAH40M. Bank 0 at low level and IPL ROM is selected at AB15.                                                                         |

| 47      | G           | _      | Ground                                                                                                                                                                          |

| 48      | 4.9 M       | Out    | Clock output gained by dividing 9.8 MHz clock. Supplied to SED1320.                                                                                                             |

| 49      | 9.8 M       | In     | Clock input of 9.8404 MHz                                                                                                                                                       |

| 50      | 2.45 M      | Out    | Clock output by dividing 9.8 MHz clock into four. Clock for main CPU.                                                                                                           |

| 51      | 1KC         | Out    | Clock output by dividing 32 KHz clock to 32. Clock for sub-CPU 7508.                                                                                                            |

| 52      | TEST        | In     | Test terminal. Normally kept low.                                                                                                                                               |

| 53      | OFF         | In     | Initializes signal for the whole internal circuit. At high level, initializes all FFs. Hold 4.9 M, 2.45 M, CS ROM, RD and Z-INT at high level and others inactive. Outputs RSO. |

| 54      | 32K         | In     | Basic clock input of 32.768 KHz. Generates 1 KC (Clock).                                                                                                                        |

| 55      | DW          | In     | Data write signal. W1 (write enable) control data supplied from sub-CPU 7508 when main CPU is on standby.                                                                       |

| 56      | DCAS        | In     | Data CAS. CAS 1 control data supplied from sub-CPU 7508 when main CPU is standby.                                                                                               |

| 57      | N/C         | _      | Not used                                                                                                                                                                        |

| 58      | N/C         | _      | Not used                                                                                                                                                                        |

| Pin No. | Signal Name | In/Out | Function                             |

|---------|-------------|--------|--------------------------------------|

| 59      | N/C         | _      | Not used                             |

| 60      | N/C         | _      | Not used                             |

| 61      | N/C         | _      | Not used                             |

| 62      | N/C         | _      | Not used                             |

| 63      | N/C         | _      | Not used                             |

| 64      | BK2         | In     | DRAM select signal from option unit. |

| 65      | VC          | _      | Circuit voltage (+5V)                |

| 66      | AB 10       | In     | Address bus 10                       |

| 67      | AB 9        | In     | Address bus 9                        |

| 68      | AB8         | In     | Address bus 8                        |

| 69      | AB 11       | In     | Address bus 11                       |

| 70      | AB 7        | ln     | Address bus 7                        |

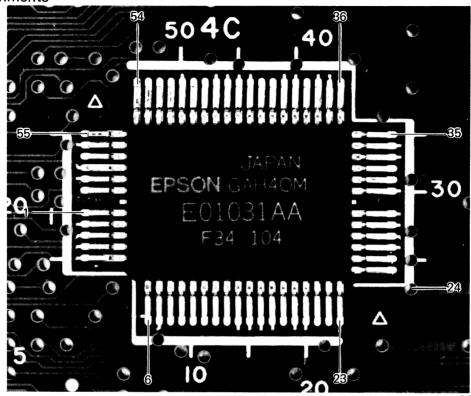

# **7.5 Gate Array GAH40M (E01031AA)**

This gate array incorporates the following functional blocks; the operation is controlled by the Z80 main CPU.

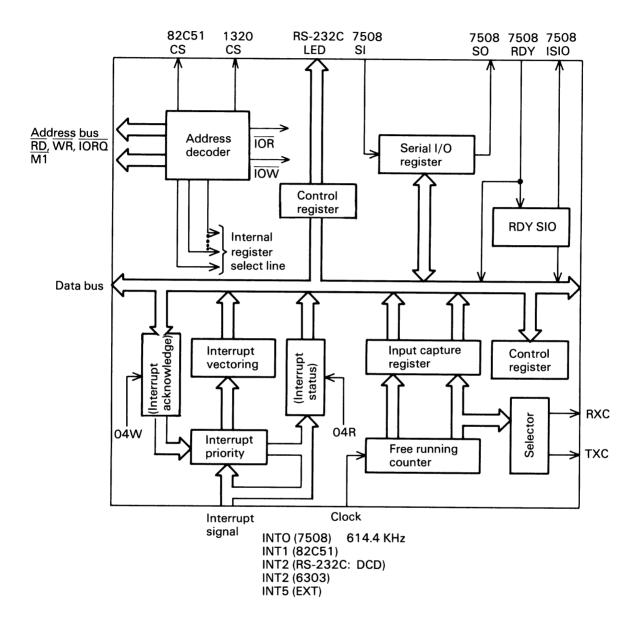

Fig. 7-5

As shown in Fig. 7-5, this gate array includes the address decoder, the 7508 interface, an interrupt controller, a timer and baud rate generator, and I/O ports for the RS-232C and the LED display.

# Table 7-6

|      | l al                                     |

|------|------------------------------------------|

|      | Write                                    |

| 00 ( | CTLR1                                    |

| 7    | BRG 3 Baud rate generator select 3 timer |

| 6    | BRG 2 Baud rate generator select 2 timer |

| 5    | BRG 1 Baud rate generator select 1 timer |

| 4    | BRG 0 Baud rate generator select 0 timer |

| 3    | SWBCD Barcode reader switch timer        |

| 2    | BCD1 (μp) Barcode mode select 1 timer    |

| 1    | BCK0 (down) Barcode mode select 0 timer  |

| 0    | BANKO Bank switching                     |

| 01 ( | CMDR                                     |

| 7    |                                          |

| 6    |                                          |

| 5    |                                          |

| 4    |                                          |

| 3    |                                          |

| 2    | 1: reset OVF(Pulse) timer                |

| 1    | 1: reset RDYSIOFF(Pulse) SIQ             |

| 0    | 1: set RDYSIOFF (Pulse) SIQ              |

| 02 ( | CTLR2                                    |

| 7    |                                          |

| 6    |                                          |

| 5    | AUX External auxiliary output            |

| 4    | INHRS Inhibit RS-232C RS232              |

| 3    | SWRS RS-232C switch RS232                |

| 2    | LED2 LED                                 |

| 1    | LED1 LED                                 |

| 0    | LEDO LED                                 |

| 03   |                                          |

|      |                                          |

|      |                                          |

|      |                                          |

|      |                                          |

|      |                                          |

|      |                                          |

|      |                                          |

|      |                                          |

|      | Read        |  |  |  |

|------|-------------|--|--|--|

| 00 1 | 00 ICLR · C |  |  |  |

| 7    | ICR7        |  |  |  |

| 6    | ICR6        |  |  |  |

| 5    | ICR5        |  |  |  |

| 4    | ICR4        |  |  |  |

| 3    | ICR3        |  |  |  |

| 2    | ICR2        |  |  |  |

| 1    | ICR1        |  |  |  |

| 0    | ICRO        |  |  |  |

| 01 I | CRH · C     |  |  |  |

| 7    | ICR15       |  |  |  |

| 6    | ICR14       |  |  |  |

| 5    | ICR13       |  |  |  |

| 4    | ICR12       |  |  |  |

| 3    | ICR11       |  |  |  |

| 2    | ICR10       |  |  |  |

| 1    | ICR9        |  |  |  |

| 0    | ICR8        |  |  |  |

| 02 I | CRL · B     |  |  |  |

| 7    | ICR7        |  |  |  |

| 6    | ICR6        |  |  |  |

| 5    | ICR5        |  |  |  |

| 4    | ICR4        |  |  |  |

| 3    | ICR3        |  |  |  |

| 2    | ICR2        |  |  |  |

| 1    | ICR1        |  |  |  |

| 0    | ICRO        |  |  |  |

| 03 1 | CRH · B     |  |  |  |

| 7    | ICR15       |  |  |  |

| 6    | ICR14       |  |  |  |

| 5    | ICR13       |  |  |  |

| 4    | ICR12       |  |  |  |

| 3    | ICR11       |  |  |  |

| 2    | ICR10       |  |  |  |

| 1    | ICR9        |  |  |  |

| 0    | ICR8        |  |  |  |

|      | Write                   |

|------|-------------------------|

| 04 1 | ER                      |

| 7    |                         |

| 6    |                         |

| 5    | IER5 (INTEXT enable)    |

| 4    | IER4 (INTOVF enable)    |

| 3    | IER3 (INTICF enable)    |

| 2    | IER2 (INT 6303 enable)  |

| 1    | IER1 (INT 82C51 enable) |

| 0    | IERO (INT 7508 enable)  |

| 05   |                         |

|      |                         |

|      |                         |

| 06 9 | SIOR                    |

| 7    | SIO 7                   |

| 6    | SIO 6                   |

| 5    | SIO 5                   |

| 4    | SIO 4                   |

| 3    | SIO 3                   |

| 2    | SIO 2                   |

| 1    | SIO 1                   |

| 0    | SIO 0                   |

| 07   |                         |

|      |                         |

|      | Read              |                |                  |  |

|------|-------------------|----------------|------------------|--|

| 04 1 | 04 ISR            |                |                  |  |

| 7    | 0                 |                |                  |  |

| 6    | 0                 |                |                  |  |

| 5    | INT 5 (INTEXT)    | External inter | rupt             |  |

| 4    | INT 4 (OVF)       | Overflow flag  | timer            |  |

| 3    | INT 3 (ICF)       | Input capture  | flag timer       |  |

| 2    | INT 2 (INT 6303)  | 6303 interrup  | ot               |  |

| ①    | INT 1 (INT 82C51) | 82C51 interre  | upt              |  |

| 0    | INTO (INT7508)    | 7:             | 508 interrupt    |  |

| 05 8 | STR               |                |                  |  |

| 7    |                   |                |                  |  |

| 6    |                   |                |                  |  |

| 5    |                   |                |                  |  |

| 4    |                   |                |                  |  |

| 3    | RDYSIO            | SIO ready      | SIO              |  |

| 2    | RDY               | ready          | SIO              |  |

| 1    | BRDT              | Barcode read   | er data timer    |  |

| 0    | BANKO             | BANKO          |                  |  |

| 06 8 | SIOR              |                |                  |  |

| 7    | SIO 7             |                |                  |  |

| 6    | SIO 6             |                |                  |  |

| 5    | SIO 5             |                |                  |  |

| 4    | SIO 4             |                |                  |  |

| 3    | SIO 3             |                |                  |  |

| 2    | SIO 2             |                |                  |  |

| 1    | SIO 1             |                |                  |  |

| 0    | SIO 0             |                |                  |  |

| 07   |                   |                | During interrupt |  |

|      |                   |                | 1                |  |

|      |                   |                | 1                |  |

|      |                   |                | 1                |  |

|      |                   |                | 1                |  |

|      |                   |                | Vect 2           |  |

|      | Interrup          | t vectoring    | Vect 1           |  |

|      |                   |                | Vect             |  |

|      |                   |                |                  |  |

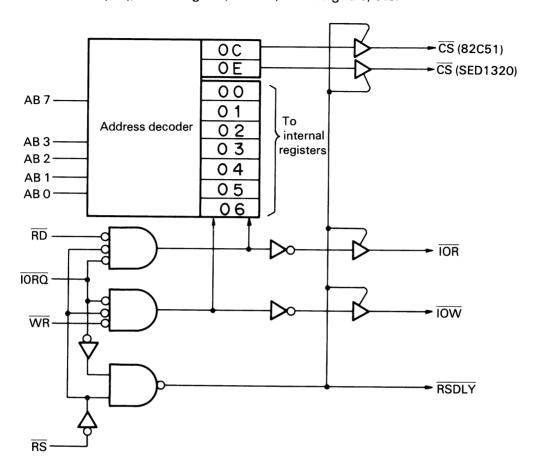

#### (1) Address Decoder

The address decoder performs each register specification, chip select signal output control of 82C51 (2C) and SED1320 (7C), decoding of I/O read/write signals, etc.

Fig. 7-6

As shown in Figure 7-6, the main CPU can directly select internal registers via four address lines. The CS signals of the 82C51 and SED1320 are also controlled by the I/O address decoder via this registers.

#### (2) Interrupt Controller

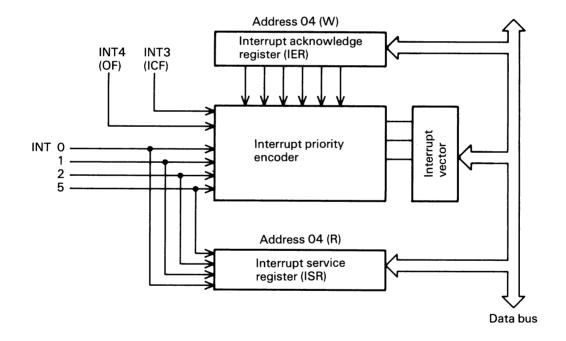

Fig. 7-7 shows six kinds of interrupt input, two of which are used for internal timer interrupt. Priority and vector addresses are assigned to each interrupt signal as shown in the table below.

**Table 7-7 Priority and Vector Addresses**

| Prior-<br>ity | Signal<br>Name | Description                                                  | Interrupt vector D7 6 5 4 3 2 1 0 | Corresponding<br>mask IER (04) | Corresponding status ISR (04) |

|---------------|----------------|--------------------------------------------------------------|-----------------------------------|--------------------------------|-------------------------------|

| Low           | ĪNT5           | (INTEXT) External pin: request from external expansion board | 11111010                          | IER5                           | ISR5                          |

|               | INT4           | (OVF) Inside: FRC overflow                                   | 11111000                          | IER4                           | ISR4                          |

|               | INT3           | (ICF) Inside: ICR bar code trigger                           | 11110110                          | IER3                           | ISR3                          |

|               | INT2           | (INT6303) External pin: request from 6303                    | 11110100                          | IER2                           | ISR2                          |

|               | INT1           | (INT82C51) External pin: request from 82C51                  | 11110010                          | IER1                           | ISR1                          |

| High          | ĪNTO           | (INT7508) External pin: request from 7508                    | 11110000                          | IERO                           | ISRO                          |

Fig. 7-7

This interrupt controller controls each interrupt acknowledge and mask operation at bit setting for IER. When an interrupt occurs, a vector address is output on the data bus.

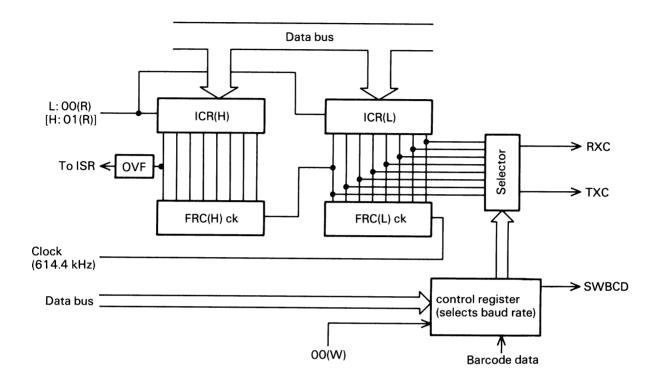

## (3) Timer and baud rate generator

An 2.4576 MHz clock supplied from the outside is divided into a basic clock of 614.4 KHz (1.6276  $\mu$ sec) which operates the free running counter (FRC). FRC is a counter of 16 bits; the low-order, 8 bit output of the FRC Cover is also used for the RS-232C transmit/ receive clock.

Fig. 7-8

When reading the content of FRC, it is necessary to latch the content to ICR (Input Capture Register) by reading address 00H. Because the counter consists of 16 bits, address 00H (low-order 8 bits) and 0IH (high-order 8 bits) must be read separately.

Bits 1 and 2, set to the control register, combined with input data cause a trigger signal from BRDT; this signal allows data going to ICR from FRC to be latched.

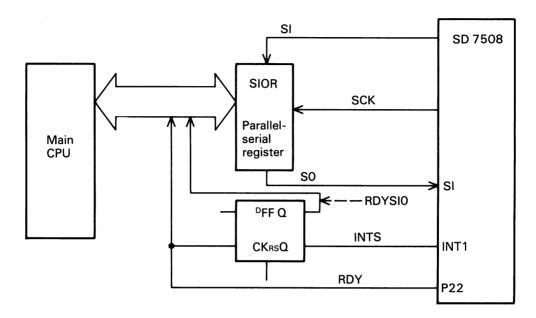

#### (4) 7508 interface

The 7508 interface contains the circuitry for handshaking between the parallel-serial converting register on the main CPU and 7508.

Fig. 7-9

Handshaking is performed in the internal flip-flop. When it is set, it means that the main CPU can access SIOR. When it is reset, it means that an interrupt signal is sent to the 7508 and the command set at SIOR is read by the 7508. The internal flip-flop is controlled by bits 0 and 1 of address OIH.

After the R/W operation to/from SIOR is completed, the set status must be changed by writing to address OIH.

Table 7-8

| Address OIH<br>Bit 1 | Reset<br>RDYSI0 | The main CPU sets a command to SIOR and requests processing to 7508. |

|----------------------|-----------------|----------------------------------------------------------------------|

| Address OIH<br>Bit O | Set<br>RDYSI0   | The power is turned on and access to 7508 is completed.              |

#### (5) I/O port

Power supply for the RS-232C, memory bank switching, and LED display on keyboard are controlled through the I/O port.

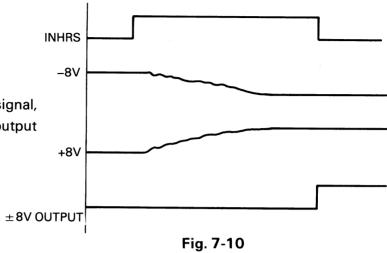

(RS-232C)

Fig. 7-10 controls power increases

The bits 3 and 4 of I/O address 02H.

$\pm 8V$  output is controlled by the INHRS signal, and is performed in order to inhibit output voltage on the line during saturation time.

#### (Bank switch)

The address space of the main CPU can be changed using bit 0 of I/O address 00H as shown below.

#### (LED display)

ON/OFF operation of shift mode LED on the keyboard is controlled using bits 0 to 2 of address 02H. (Bit ON drives the corresponding LED.)

#### **GAH40M**

1. Location: MAPLE Board, 4C

2. Pin assignments

Note: Pins 25 and 59 are cut.

**Table 7-9 GAH40M Pin Assignments**

| Table 7-3 dari-town in Assignments |             |        |                                                                                             |  |

|------------------------------------|-------------|--------|---------------------------------------------------------------------------------------------|--|

| Pin No.                            | Signal Name | In/Out | Function                                                                                    |  |

| 1                                  | DB6         | In/Out | Data bus 6                                                                                  |  |

| 2                                  | DB1         | In/Out | Data bus 1                                                                                  |  |

| 3                                  | ĪR          | Out    | Indicates that data is being output according to main CPU instruction (RS-232C → main CPU). |  |

| 4                                  | DB 0        | In/Out | Data bus 0                                                                                  |  |

| 5                                  | DB 2        | In/Out | Data bus 2                                                                                  |  |

| 6                                  | CSOE        | Out    | SED1320 chip select signal                                                                  |  |

| 7                                  | RS          | In     | Reset input: Supplied from GAH40D.                                                          |  |

| 8                                  | ĪW          | Out    | Indicates that data is being input according to main CPU instruction (main CPU → RS-232C).  |  |

| 9                                  | N/C         | _      | Not used.                                                                                   |  |

| 10                                 | TXC         | Out    | Baud rate control clock (for RS-232C).                                                      |  |

| Pin No. | Signal Name | In/Out | Function                                                                                         |

|---------|-------------|--------|--------------------------------------------------------------------------------------------------|

| 11      | ĪNTO        | In     | Sub-CPU 7508 interrupt signal                                                                    |

| 12      | SWBCD       | Out    | Barcode power supply (+5V) switching signal                                                      |

| 13      | RXC         | Out    | Clock which controls receive character synchronization (RS-232C).                                |

| 14      | BCD         | In     | Bar code read data                                                                               |

| 15      | CSIO        | In     | HIGH: Indicates that sub-CPU 7508 can access SIOR.  LOW: Indicates that main CPU can read/write. |

| 16      | SI          | In     | Serial data input from sub-CPU 7508.                                                             |

| 17      | SO          | Out    | Serial data output to sub-CPU 7508.                                                              |

| 18      | S-INT       | Out    | Interrupt signal to main CPU. Gives an interrupt via GAH40D (Z-INT signal).                      |

| 19      | DB 5        | In/Out | Data bus 5                                                                                       |

| 20      | DB 3        | In/Out | Data bus 3                                                                                       |

| 21      | N/C         | _      | Not used.                                                                                        |

| 22      | N/C         | _      | Not used.                                                                                        |

| 23      | N/C         | _      | Not used.                                                                                        |

| 24      | N/C         | _      | Not used.                                                                                        |

| 25      | N/C         | _      | Not used.                                                                                        |

| 26      | SWRS        | Out    | Switching signal for RS-232C power supply                                                        |

| 27      | INHRS       | Out    | Controls output voltage during power saturation time of RS-232C.                                 |

| 28      | OFF         | In     | Power off. To prevent latch-up by isolating output in high impedance.                            |

| 29      | G           | _      | Ground                                                                                           |

| 30      | TEST        | In     | Test terminal. Normally kept low level.                                                          |

| 31      | N/C         | _      | Not used.                                                                                        |

| 32      | AUX         | Out    | RS-232C transmit/receive line control                                                            |

| Pin No. | Signal Name | In/Out | Function                                                                                               |

|---------|-------------|--------|--------------------------------------------------------------------------------------------------------|

| 33      | INT 1       | ln     | Serial controller 82C51 interrupt signal                                                               |

| 34      | INT 5       | ln     | Interrupt signal from option unit                                                                      |

| 35      | N/C         | _      | Not used.                                                                                              |

| 36      | SCK         | ln     | Data transmit/receive shift clock against SIOR register. Provided from sub-CPU 7508.                   |

| 37      | INT 2       | In     | RS-232C CD signal interrupt signal                                                                     |

| 38      | RD          | . In   | Read signal: Synchronized to AND of IORQ. Outputs data on data bus.                                    |

| 39      | AB 1        | ln     | Address bus 1                                                                                          |

| 40      | WR          | ln     | Write signal: Synchronized to AND of IORQ. Outputs data on data bus.                                   |

| 41      | INTS        | Out    | Interrupt signal to sub-CPU 7508                                                                       |

| 42      | AB O        | In     | Address bus 0                                                                                          |

| 43      | RDY         | ln     | Ready signal of sub-CPU                                                                                |

| 44      | LED 2       | Out    | Lamp control signal of LED on keyboard (lowest of the three)                                           |

| 45      | AB 7        | ln     | Address bus 7                                                                                          |

| 46      | LED 1       | Out    | Lamp control signal of LED on keyboard (highest of the three)                                          |

| 47      | LED O       | Out    | Lamp control signal of LED on keyboard (center of the three)                                           |

| 48      | ĪORQ        | ln     | Main CPU in MI cycle: Request to output interrupt response vector on data bus.                         |

| 49      | AB 2        | In     | Address bus 2                                                                                          |

| 50      | CSOC        | Out    | Serial controller 82C51 chip select signal.                                                            |

| 51      | BANKO/1     | Out    | Bank select signal                                                                                     |

| 52      | M1          | ln     | Main CPU in machine cycle 1: Interrupt response vector is read to main CPU by AND operation with IORQ. |

| 53      | N/C         | _      | Not used.                                                                                              |

| Pin No. | Signal Name | In/Out       | Function                                                         |

|---------|-------------|--------------|------------------------------------------------------------------|

| 54      | N/C         | <del>-</del> | Not used.                                                        |

| 55      | N/C         | -            | Not used.                                                        |

| 56      | DB 4        | In/Out       | Data bus 4                                                       |

| 57      | AB 7        | In           | Address bus 27                                                   |

| 58      | DB 7        | In/Out       | Data bus.                                                        |

| 59      | 2.45        | ln           | 2.45 MHz clock on which timer and baud rate generator are based. |

| 60      | VC          | _            | Circuit voltage (+5V)                                            |

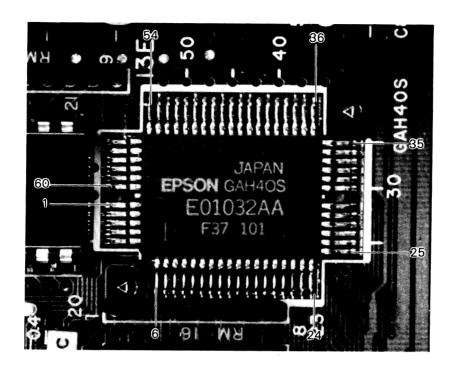

# 7.6 Gate Array GAH40S

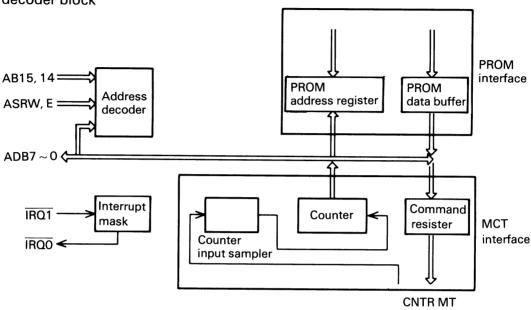

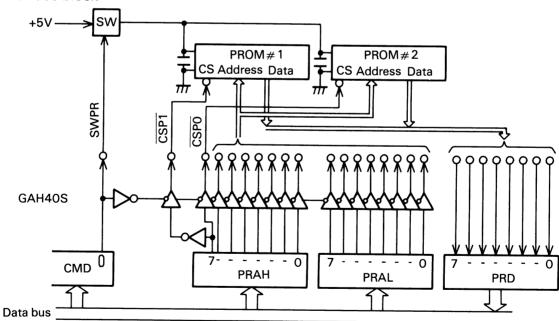

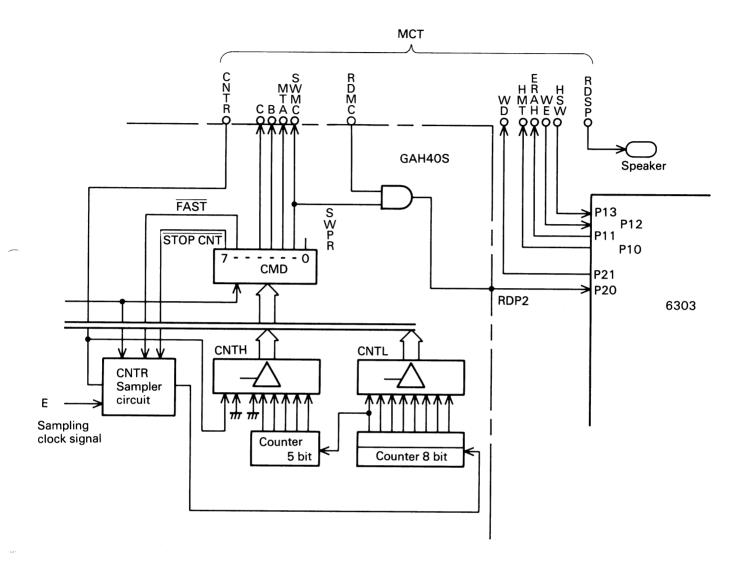

Gate array GAH40S, which is controlled by the 6303 slave CPU, in turn controls the microcassette tape drive, LCD controller, and ROM capsule. It consists of three segments: an address decoder, a microcassette tape drive interface, and a P-ROM interface. Figs. 7-12 through 7-14 are functional block diagrams of these blocks.

#### (1) Address decoder block

Fig. 7-12 Address decoder block diagram

#### (2) P-ROM interface block

Fig. 7-13 P-ROM Interface Block Diagram

# (3) Microcassette tape drive interface block

Fig. 7-14 Microcassette Tape Drive Interface Block Diagram

## **GAH40S**

- Location: MAPLE Board, 13E

Pin assignments

Note: Pins 25, 27 are cut.

**Table 7-10 GAH40S Pin Assignments**

| Pin No. | Signal Name | In/Out | Function        |

|---------|-------------|--------|-----------------|

| 1       | PRA 12      | Out    | PROM address 12 |

| 2       | PRA 14      | Out    | PROM address 14 |

| 3       | PRA 7       | Out    | PROM address 7  |

| 4       | PRA 13      | Out    | PROM address 13 |

| 5       | PRA 6       | Out    | PROM address 6  |

| 6       | PRA 8       | Out    | PROM address 8  |

| 7       | PRA 11      | Out    | PROM address 11 |

| 8       | PRA 4       | Out    | PROM address 4  |

| 9       | PRA 9       | Out    | PROM address 9  |

| 10      | PRA 5       | Out    | PROM address 5  |

| 11      | PRA 10      | Out    | PROM address 10 |

| 12      | PRA 3       | Out    | PROM address 3  |

| 13      | PRA 2       | Out    | PROM address 2  |

| 14         CSP1         Out         PROM chip select.           15         PRD 0         In         PROM data 0           16         CSP0         Out         Chip select           17         PRD 7         In         PROM data 7           18         PRA 1         Out         PROM data 7           19         PRA 0         Out         PROM address 0           20         PRD 6         In         PROM data 6           21         PRD 1         In         PROM data 1           22         PRD 4         In         PROM data 4           23         PRD 3         In         PROM data 3           24         PRD 2         In         PROM data 3           24         PRD 5         In         PRD data 5           26         MTDA         Out         Microcassette drive motor control signal A           27         MTDB         Out         Microcassette drive motor control signal B           28         MTDC         Out         Microcassette drive motor control signal C           29         G         -         Ground           30         N/C         -         Not used           31         SWMCT         Out <th>Pin No.</th> <th>Signal Name</th> <th>In/Out</th> <th>Function</th>                                          | Pin No. | Signal Name | In/Out | Function                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|--------|--------------------------------------------|

| 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14      | CSP 1       | Out    | PROM chip select.                          |

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15      | PRD 0       | In     | PROM data 0                                |

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16      | CSP 0       | Out    | Chip select                                |

| 19         PRA 0         Out         PROM address 0           20         PRD 6         In         PROM data 6           21         PRD 1         In         PROM data 1           22         PRD 1         In         PROM data 4           23         PRD 3         In         PROM data 3           24         PRD 2         In         PROM data 2           25         PRD 5         In         PRD data 5           26         MTDA         Out         Microcassette drive motor control signal A           27         MTDB         Out         Microcassette drive motor control signal B           28         MTDC         Out         Microcassette drive motor control signal C           29         G         —         Ground           30         N/C         —         Not used           31         SWMCT         Out         Microcassette power switch           32         CNTR         In         Counter signal from microcassette           33         RDMC         In         Microcassette read data           34         CSLV         Out         SED1320 VRAM chip select signal. Low level when addresses 8000 to BFFF are specified.           35         N/C         — <td>17</td> <td>PRD 7</td> <td>In</td> <td>PROM data 7</td> | 17      | PRD 7       | In     | PROM data 7                                |

| PRD 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18      | PRA 1       | Out    | PROM address 1                             |

| 21         PRD 1         In         PROM data 1           22         PRD 4         In         PROM data 4           23         PRD 3         In         PROM data 3           24         PRD 2         In         PROM data 2           25         PRD 5         In         PRD data 5           26         MTDA         Out         Microcassette drive motor control signal A           27         MTDB         Out         Microcassette drive motor control signal B           28         MTDC         Out         Microcassette drive motor control signal C           29         G         -         Ground           30         N/C         -         Not used           31         SWMCT         Out         Microcassette power switch           32         CNTR         In         Counter signal from microcassette           33         RDMC         In         Microcassette read data           34         CSLV         Out         SED1320 VRAM chip select signal. Low level when addresses 8000 to BFFF are specified.           35         N/C         -         Not used.           36         CSLC         Out         SED1320 internal register select signal. Low level when addresses 0024 to 0027 are specified.                       | 19      | PRA 0       | Out    | PROM address 0                             |

| 22         PRD 4         In         PROM data 4           23         PRD 3         In         PROM data 3           24         PRD 2         In         PROM data 2           25         PRD 5         In         PRD data 5           26         MTDA         Out         Microcassette drive motor control signal A           27         MTDB         Out         Microcassette drive motor control signal B           28         MTDC         Out         Microcassette drive motor control signal C           29         G         -         Ground           30         N/C         -         Not used           31         SWMCT         Out         Microcassette power switch           32         CNTR         In         Counter signal from microcassette           33         RDMC         In         Microcassette read data           34         CSLV         Out         SED1320 VRAM chip select signal. Low level when addresses 8000 to BFFF are specified.           35         N/C         -         Not used.           36         CSLC         Out         SED1320 internal register select signal. Low level when addresses 0024 to 0027 are specified.           37         AB15         In         Slave CPU address 15<              | 20      | PRD 6       | In     | PROM data 6                                |

| 23         PRD 3         In         PROM data 3           24         PRD 2         In         PROM data 2           25         PRD 5         In         PRD data 5           26         MTDA         Out         Microcassette drive motor control signal A           27         MTDB         Out         Microcassette drive motor control signal B           28         MTDC         Out         Microcassette drive motor control signal C           29         G         -         Ground           30         N/C         -         Not used           31         SWMCT         Out         Microcassette power switch           32         CNTR         In         Counter signal from microcassette           33         RDMC         In         Microcassette read data           34         CSLV         Out         SED1320 VRAM chip select signal. Low level when addresses 8000 to BFFF are specified.           35         N/C         -         Not used.           36         CSLC         Out         SED1320 internal register select signal. Low level when addresses 0024 to 0027 are specified.           37         AB15         In         Slave CPU address 15           38         AB14         In         Slave CPU add              | 21      | PRD 1       | In     | PROM data 1                                |

| 24         PRD 2         In         PROM data 2           25         PRD 5         In         PRD data 5           26         MTDA         Out         Microcassette drive motor control signal A           27         MTDB         Out         Microcassette drive motor control signal B           28         MTDC         Out         Microcassette drive motor control signal C           29         G         -         Ground           30         N/C         -         Not used           31         SWMCT         Out         Microcassette power switch           32         CNTR         In         Counter signal from microcassette           33         RDMC         In         Microcassette read data           34         CSLV         Out         SED1320 VRAM chip select signal. Low level when addresses 8000 to BFFF are specified.           35         N/C         -         Not used.           36         CSLC         Out         SED1320 internal register select signal. Low level when addresses 0024 to 0027 are specified.           37         AB15         In         Slave CPU address 15           38         AB14         In         Slave CPU address 15                                                                 | 22      | PRD 4       | In     | PROM data 4                                |

| 25 PRD 5 In PRD data 5 26 MTDA Out Microcassette drive motor control signal A 27 MTDB Out Microcassette drive motor control signal B 28 MTDC Out Microcassette drive motor control signal C 29 G - Ground 30 N/C - Not used 31 SWMCT Out Microcassette power switch 32 CNTR In Counter signal from microcassette 33 RDMC In Microcassette read data 34 CSLV Out SED1320 VRAM chip select signal. Low level when addresses 8000 to BFFF are specified. 35 N/C - Not used. 36 CSLC Out SED1320 internal register select signal. Low level when addresses 0024 to 0027 are specified. 37 AB15 In Slave CPU address 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23      | PRD 3       | In     | PROM data 3                                |

| MTDA Out Microcassette drive motor control signal A  MTDB Out Microcassette drive motor control signal B  MTDC Out Microcassette drive motor control signal C  Ground  N/C - Ground  Not used  N/C - Not used  CNTR In Counter signal from microcassette  RDMC In Microcassette read data  CSLV Out SED1320 VRAM chip select signal. Low level when addresses 8000 to BFFF are specified.  N/C - Not used.  CSLC Out SED1320 internal register select signal. Low level when addresses 0024 to 0027 are specified.  AB15 In Slave CPU address 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24      | PRD 2       | In     | PROM data 2                                |

| MTDB Out Microcassette drive motor control signal B  MTDC Out Microcassette drive motor control signal C  Ground  Not used  N/C - Not used  CNTR In Counter signal from microcassette  RDMC In Microcassette read data  CSLV Out SED1320 VRAM chip select signal. Low level when addresses 8000 to BFFF are specified.  Not used.  Not used.  SED1320 internal register select signal. Low level when addresses 0024 to 0027 are specified.  AB15 In Slave CPU address 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25      | PRD 5       | ln     | PRD data 5                                 |

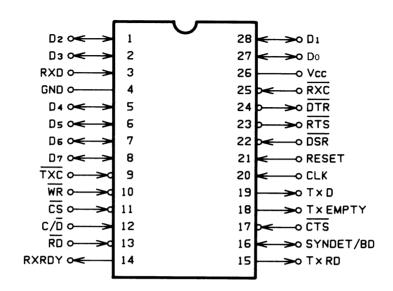

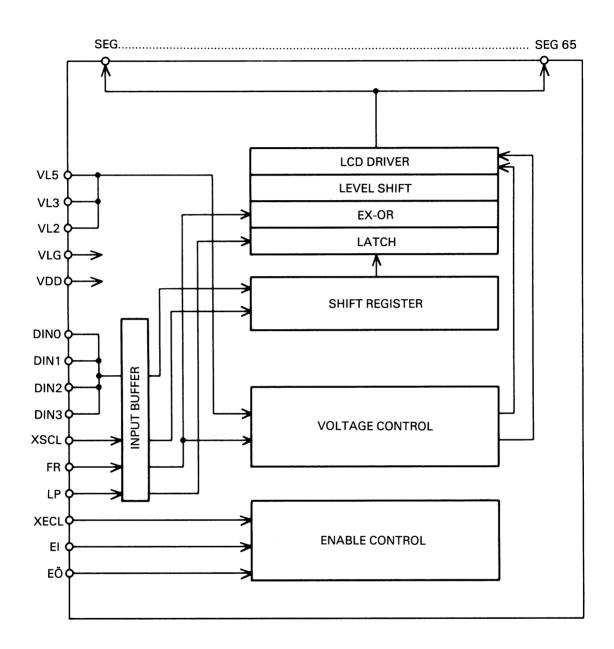

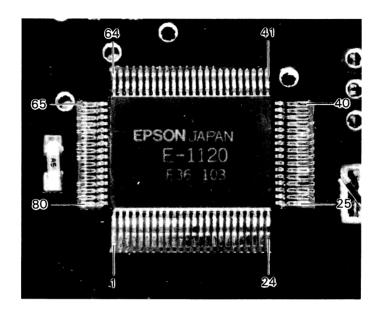

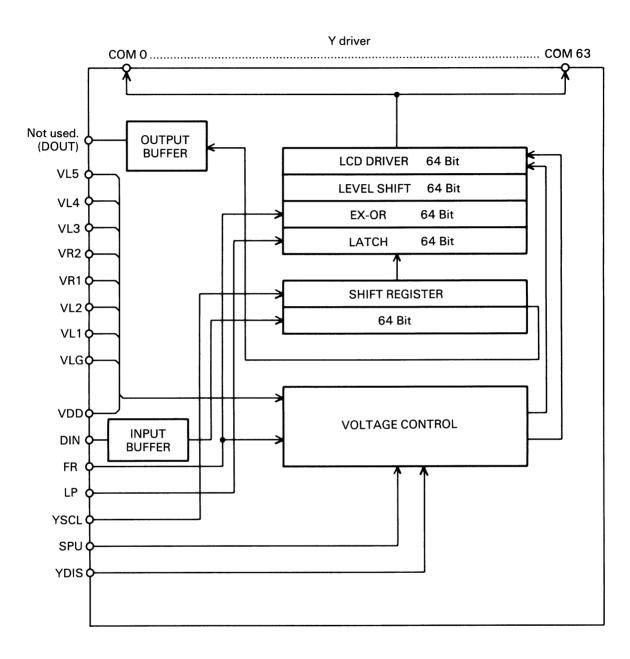

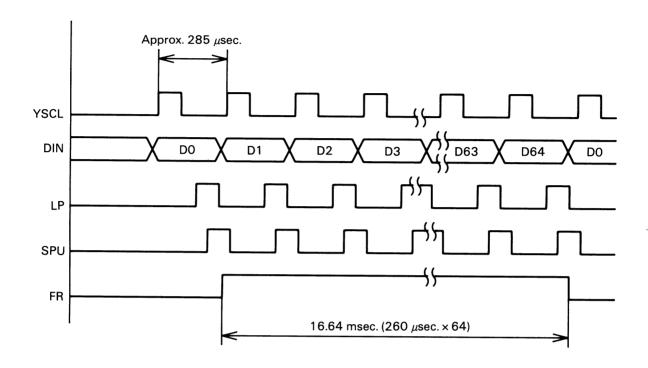

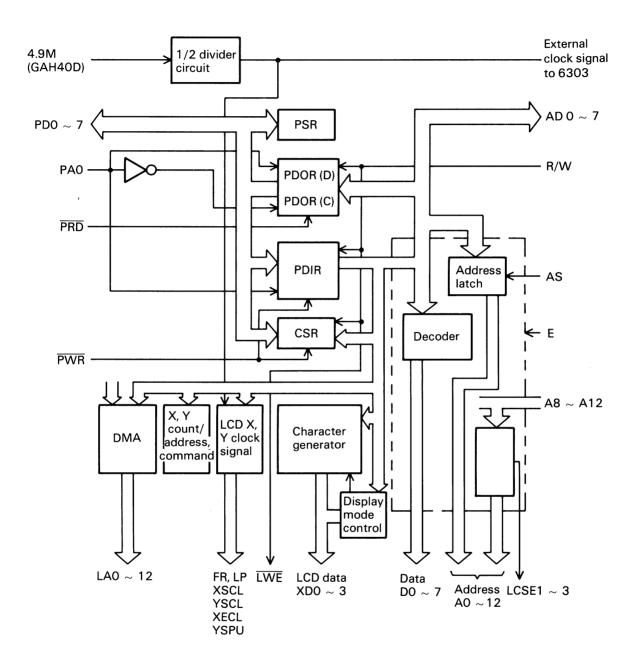

| 28 MTDC Out Microcassette drive motor control signal C 29 G - Ground 30 N/C - Not used 31 SWMCT Out Microcassette power switch 32 CNTR In Counter signal from microcassette 33 RDMC In Microcassette read data 34 CSLV Out SED1320 VRAM chip select signal. Low level when addresses 8000 to BFFF are specified. 35 N/C - Not used. 36 CSLC Out SED1320 internal register select signal. Low level when addresses 0024 to 0027 are specified. 37 AB15 In Slave CPU address 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26      | MTDA        | Out    | Microcassette drive motor control signal A |