# APPENDIX

-

----

----

-

\_

| 1. | Basic  | Information on Circuitry            |     |            |

|----|--------|-------------------------------------|-----|------------|

|    | 1.1    | Table of Binary Code                | A-  | 1          |

|    | 1.2    | Transistors and Color Code          | A-  | 2          |

|    | 1.3    | Circuit Symbols                     | A-  | 3          |

| 2. | ICs    |                                     |     |            |

|    | 2.1    | Table of Main ICs                   | A-  | 6          |

|    | 2.2    | ICs                                 | A-  | 7          |

| 3. | Serial | -Parallel Conversion                |     |            |

|    | 3.1    | Parallel to Serial Conversion       | A-2 | 22         |

|    | 3.2    | Serial to Parallel Conversion       | A-2 | 22         |

| 4. | Main   | Circuit Signals                     |     |            |

|    | 4.1    | Enable                              | A-2 | 23         |

|    | 4.2    | Address Strobe                      | A-2 | 23         |

|    | 4.3    | Address/Data Bus                    | A-2 | 23         |

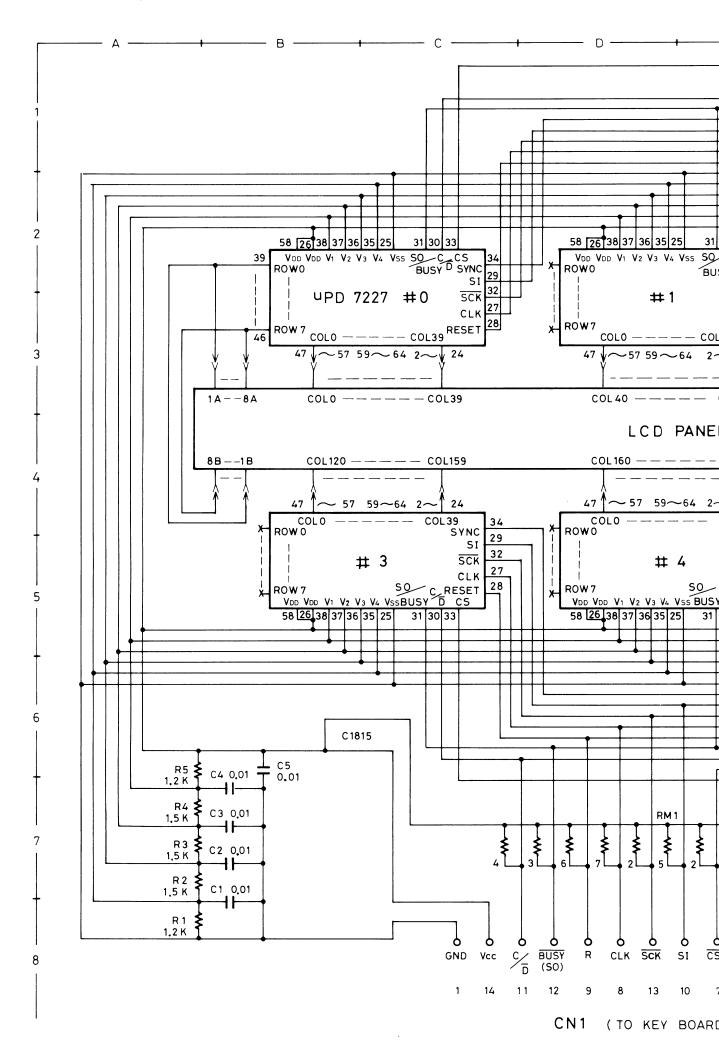

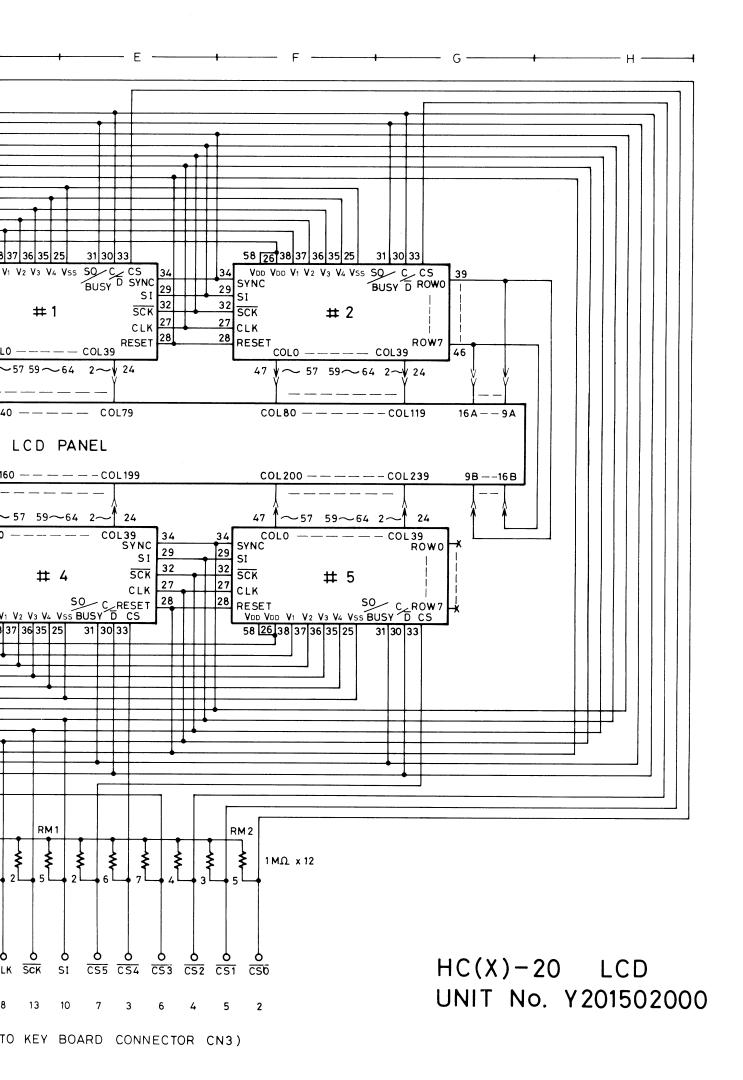

|    | 4.4    | LCD Chip Select                     | A-2 | 24         |

|    | 4.5    | LCD Shift Clock (SCK)               | A-2 | 24         |

|    | 4.6    | Clock Pulse for Clock               | A-2 | <u>2</u> 4 |

|    | 4.7    | KSC                                 | A-2 | 25         |

|    | 4.8    | Key Input Control                   | A-2 | 25         |

|    | 4.9    | KB REQUEST                          | A-2 | 25         |

|    | 4.10   | Cassette Write Waveform             | A-2 | 26         |

|    | 4.11   | Cassette Read Waveform              | A-2 | 26         |

|    | 4.12   | Cassette Read Waveform              | A-2 | 26         |

|    | 4.13   | Microcassette Read Waveform         | A-2 | 27         |

|    | 4.14   | Microcassette Read Waveform         | A-2 | 27         |

|    | 4.15   | Microcassette Tachogenerator Output | A-2 | 27         |

# 1. Basic Information on Circuitry

# 1.1 Table of Binary code

| _    |     |   | DI | ECIM | AL |   | ]    | ł               |

|------|-----|---|----|------|----|---|------|-----------------|

| A 15 | 8   | 3 | 2  | 7    | 6  | 8 | 32 K | 000             |

| A 14 | 4   | 1 | 6  | 3    | 8  | 4 | 16 K | <br>1000 ~ F000 |

| A 13 | 2   |   | 8  | 1    | 9  | 2 | 8 K  | 1000            |

| A 12 | 1   |   | 4  | 0    | 9  | 6 | 4 K  |                 |

| A 11 | 8   |   | 2  | 0    | 4  | 8 | 2 K  |                 |

| A 10 | 4   |   | 1  | 0    | 2  | 4 | 1 K  | F00             |

| A 9  | 2   |   |    | 5    | 1  | 2 |      | 100 ~ F00       |

| A 8  | . 1 |   |    | 2    | 5  | 6 |      | _               |

| A 7  | 8   |   |    | 1    | 2  | 8 |      |                 |

| A 6  | 4   |   |    |      | 6  | 4 |      | FO              |

| A 5  | 2   |   |    |      | 3  | 2 |      | $10 \sim$       |

| A 4  | 1   |   |    |      | 1  | 6 |      |                 |

| A 3  | 8   |   |    |      |    | 8 |      |                 |

| A 2  | 4   |   |    |      |    | 4 |      | (L              |

| A 1  | 2   |   |    |      |    | 2 |      | ~ 0             |

| A 0  | 1   |   |    |      |    | 1 |      |                 |

| Decimal | HEX | (Bit) Binary | Decimal | HEX | (Bit) Binary | Decimal | HEX | (Bit) binary |

|---------|-----|--------------|---------|-----|--------------|---------|-----|--------------|

| 0       | 0   | 0000         | 6       | 6   | 0110         | 12      | С   | 1100         |

| 1       | 1   | 0001         | 7       | 7   | 0111         | 13      | D   | 1101         |

| 2       | 2   | 0010         | 8       | 8   | 1000         | 14      | E   | 1110         |

| 3       | 3   | 0011         | 9       | 9   | 1001         | 15      | F   | 1111         |

| 4       | 4   | 0100         | 10      | А   | 1010         | 16      | 10  | 10000        |

| 5       | 5   | 0101         | 11      | В   | 1011         | 17      | 11  | 10001        |

#### **1.2 Transistors and Color Code**

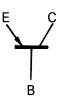

(1) Transistors

**PNP Transistor** Turned on when the base (B) is at low level.

**NPN Transistor**

Turned on when the base (B) is at high level.

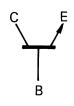

#### (2) Color markings of resistors and capacitors

#### 1.3 Circuit Symbols

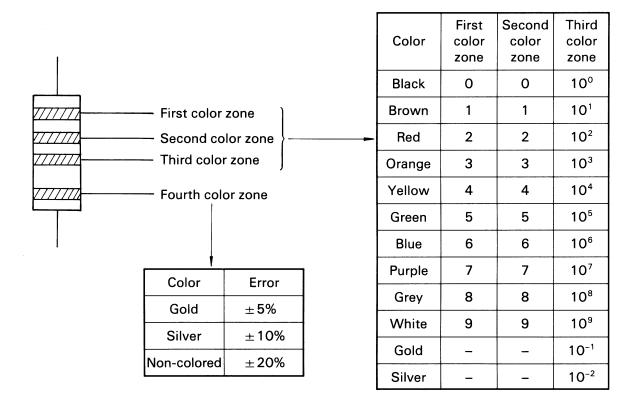

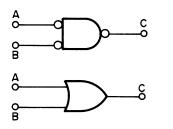

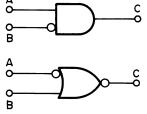

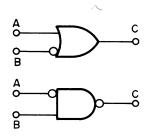

(1) AND circuit (H: High level, L: Low level)

(3) Logics of AND circuit and OR circuit

A

**Truth Table**

|   | In  | put | Output |

|---|-----|-----|--------|

|   | A B |     | С      |

| : | L   | L   | L      |

|   | Н   | L   | Н      |

|   | L   | Н   | Н      |

|   | Н   | Н   | Н      |

| In | put | Output |

|----|-----|--------|

| A  | В   | C      |

| L  | L   | L      |

| Н  | L   | Н      |

| L  | Н   | L      |

| H  | Н   | L      |

**Truth Table**

| Inj | out | Output |  |

|-----|-----|--------|--|

| Α   | В   | С      |  |

| L   | L   | Н      |  |

| H   | L   | Н      |  |

| L   | Н   | L      |  |

| Н   | H   | Н      |  |

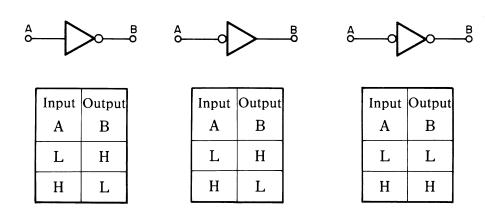

(4) Inverter circuit

Note: The circle in the symbol indicates the open collector type.

| Truth Ta | able |

|----------|------|

|----------|------|

|   |   | Ι | Ou                | tput |     |     |

|---|---|---|-------------------|------|-----|-----|

|   | Α | В | C                 | D    | Q   | Q   |

| 1 | L | Н | ×                 | ×    | Н   | L   |

| 2 | Н | L | ×                 | ×    | L   | Н   |

| 3 | L | L | ×                 | ×    | H * | H * |

| 4 | Н | Н | $L \rightarrow H$ | H    | Н   | L   |

| 5 | Н | Н | $L \rightarrow H$ | L    | L   | Н   |

| 6 | Н | H | L                 | Н    | Н   | L   |

| 7 | Н | Н | L                 | L    | L   | Н   |

\* Temporary state

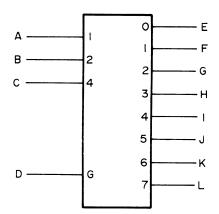

#### (6) Decoder

|   |   | Inp | out |   |   |   |   | Out | put |   |   |   |

|---|---|-----|-----|---|---|---|---|-----|-----|---|---|---|

|   | A | В   | С   | D | E | F | G | Н   | Ι   | J | K | L |

| 1 |   |     |     | L | L | L | L | L   | L   | L | L | L |

| 2 | L | L   | L   | Н | Н | L | L | L   | L   | L | L | L |

| 3 | Н | L   | L   | Н | L | Н | L | L   | L   | L | L | L |

| 4 | L | Н   | L   | Н | L | L | Н | L   | L   | L | L | L |

| 5 | Н | Н   | L   | Н | L | L | L | Н   | L   | L | L | L |

| 6 | L | L   | Н   | Н | L | L | L | L   | Н   | L | L | L |

| 7 | Н | L   | Н   | Н | L | L | L | L   | L   | Н | L | L |

| 8 | L | Н   | Н   | Н | L | L | L | L   | L   | L | Н | L |

| 9 | Н | Н   | Н   | Н | L | L | L | L   | L   | L | L | Н |

# 2. IC

## 2.1 Table of Main ICs

| Name        | Part Code  | Туре                        | Location of Use      |

|-------------|------------|-----------------------------|----------------------|

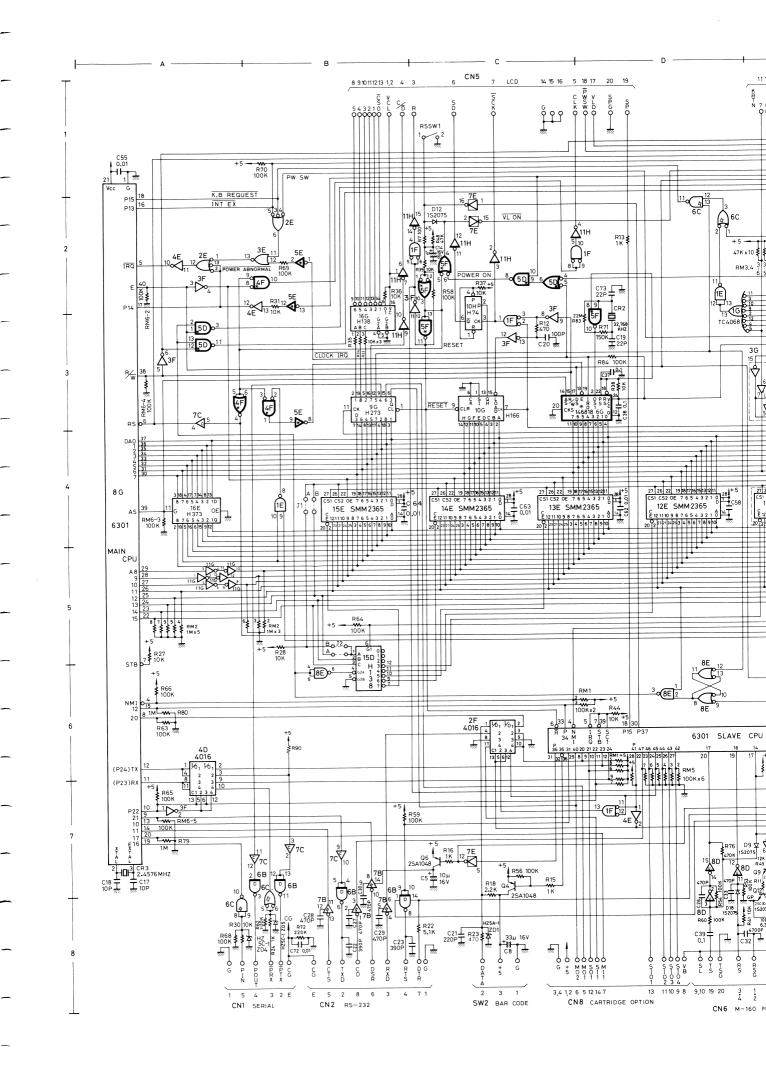

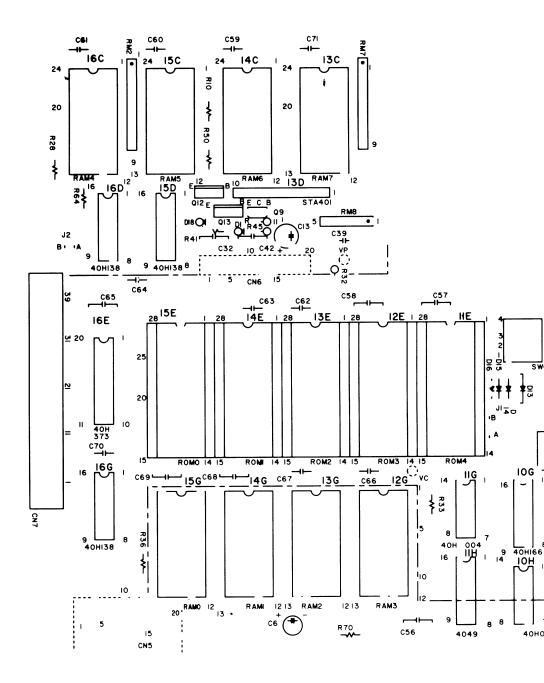

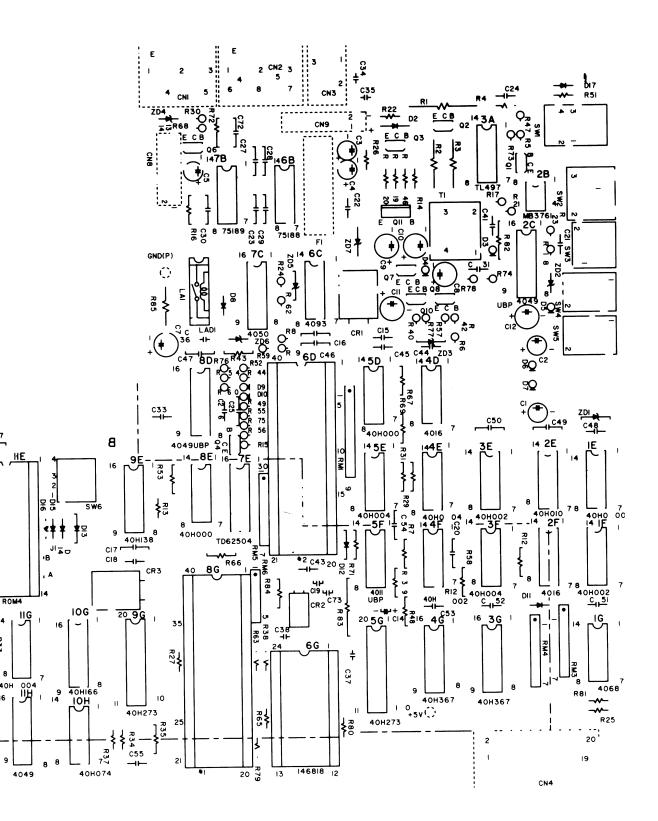

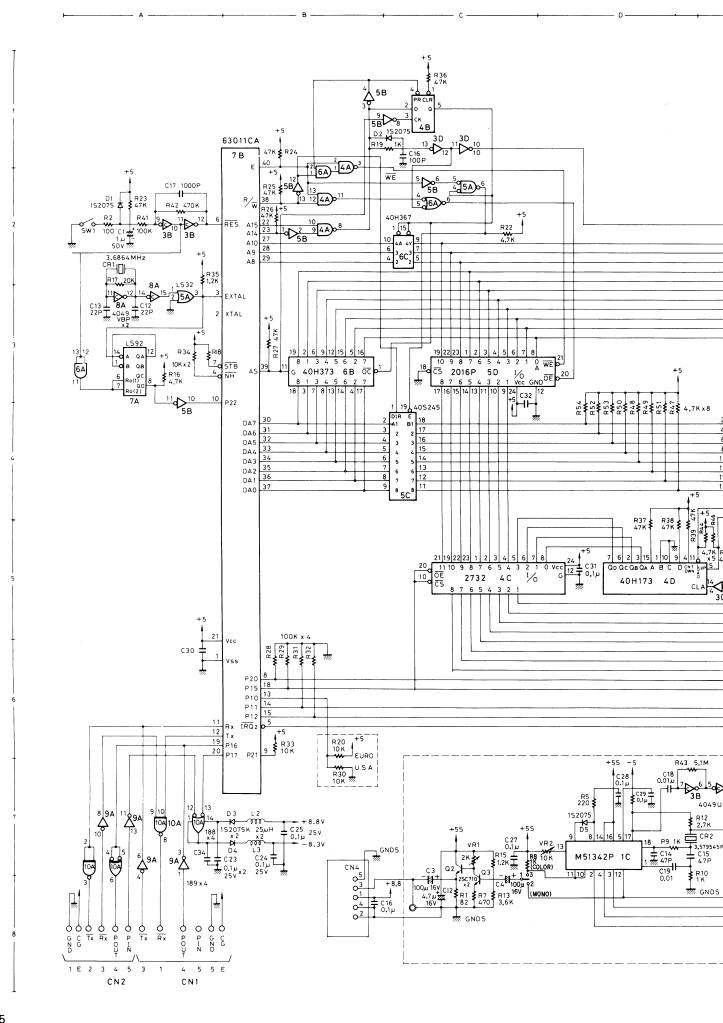

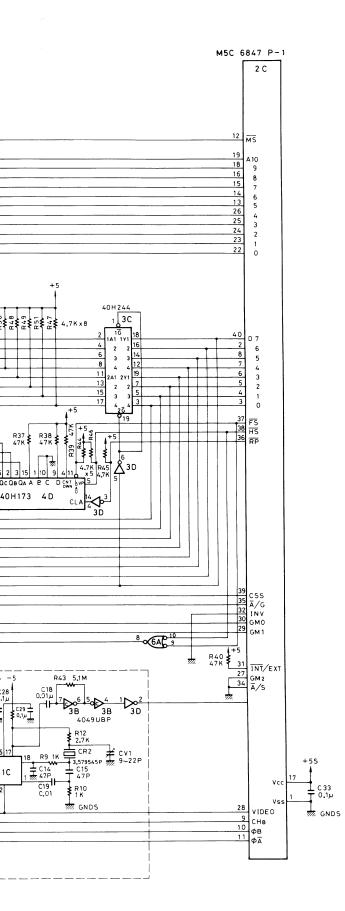

| 6301        | X40006310  | CPU (Main CPU)              | 8G                   |

| 6301 (MASK) | Y201800301 | CPU (Slave CPU)             | 6D                   |

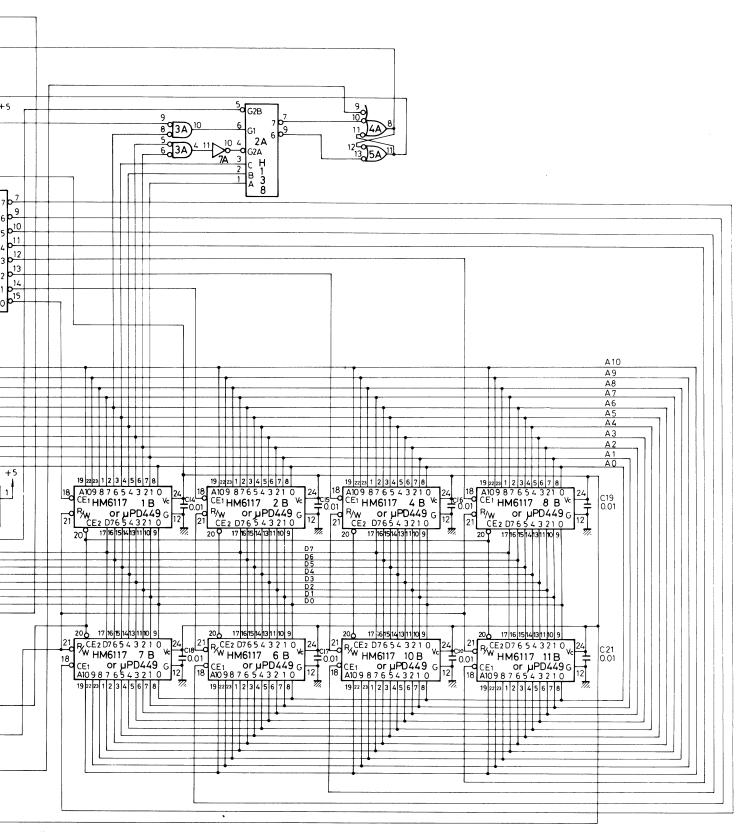

| M16010C′    | X400004491 | RAM (2K byte)               | 13C ~ 16C, 12G ~ 15G |

| MB3761      | X440167610 | OP AMP                      | 2B                   |

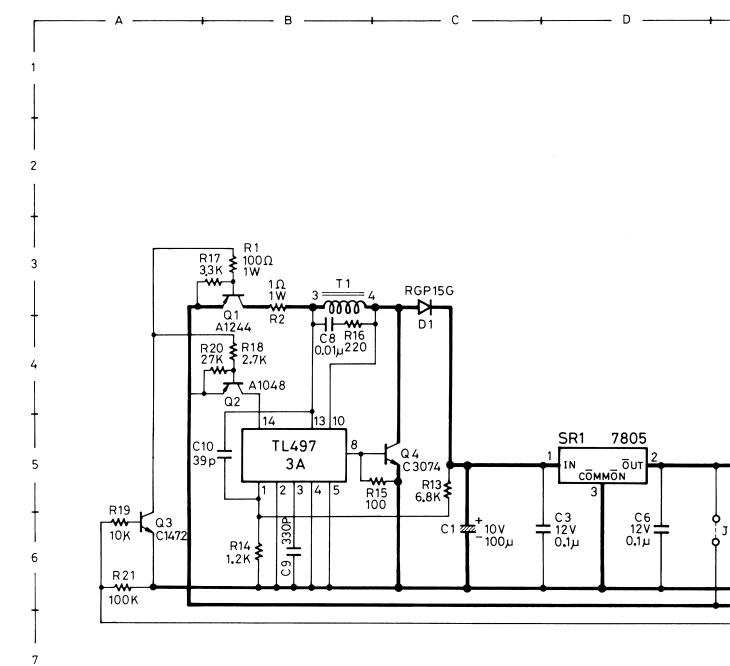

| TL497       | X440034970 | Switching voltage regulator | 3A                   |

| TD62504     | X440045040 | Driver (Transistor array)   | 7E                   |

| HD75188     | X440751880 | Line driver (for RS-232C)   | , 6B                 |

| HD75189     | X440751890 | Line receiver (for RS-232C) | 7B                   |

| TC4016BP    | X460401600 | Two-way switch              | 2F, 4D               |

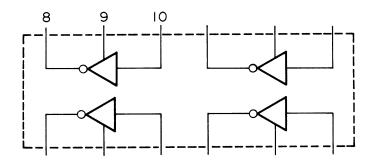

| TC4049BP    | X460404900 | Converter                   | 2C, 7C, 11H          |

| TC4068BP    | X460406800 | 8-input NAND                | 1G                   |

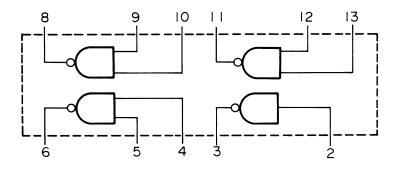

| TC4093BP    | X460409300 | 2-input NAND                | 6C                   |

| TC4011UBP   | X460401101 | 2-input NAND                | 5F                   |

| TC4049UBP   | X460404902 | Converter                   | 7C, 8D               |

| TC40H000    | X460400004 | 2-input NAND                | 1E, 5D, 8E           |

| TC40H002    | X460400204 | 2-input NOR                 | 1F, 3E, 4F           |

| TC40H004    | X460400404 | HEX INVERTER                | 3F, 4E, 5E, 11G      |

| TC40H010    | X460401004 | 3-input NAND                | 2E                   |

| TC40H074    | X460407404 | Flip-flop                   | 10H                  |

| TC40H138    | X460413804 | Decoder                     | 9E, 15D, 16D, 16G    |

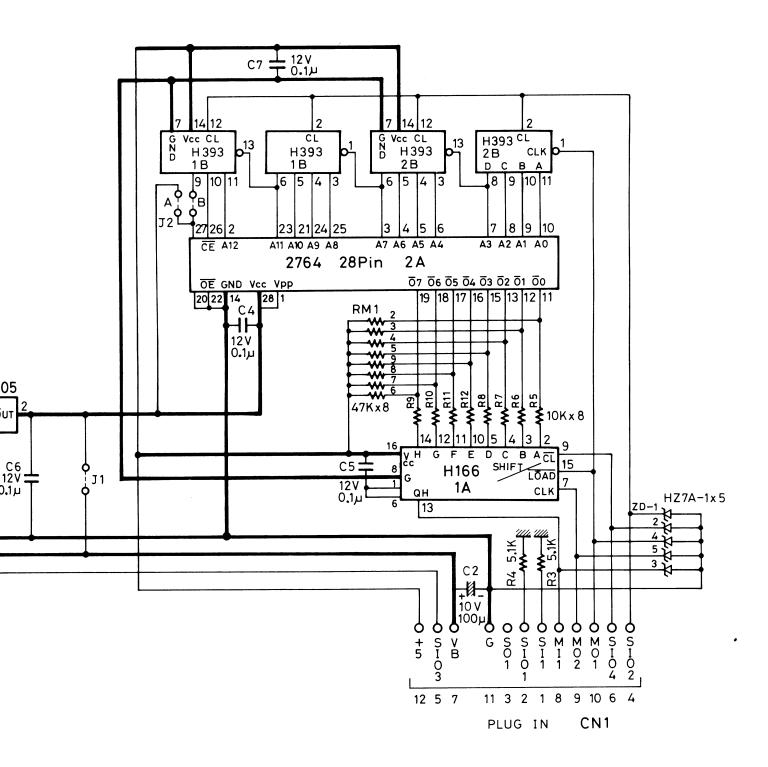

| TC40H166    | X460416604 | Shift register              | 10G                  |

| TC40H273    | X460427304 | Flip-flop                   | 5G, 9G               |

| TC40H367    | X460436704 | 3-input buffer              | 3G, 4G               |

| TC40H373    | X460437304 | Latch                       | 16E                  |

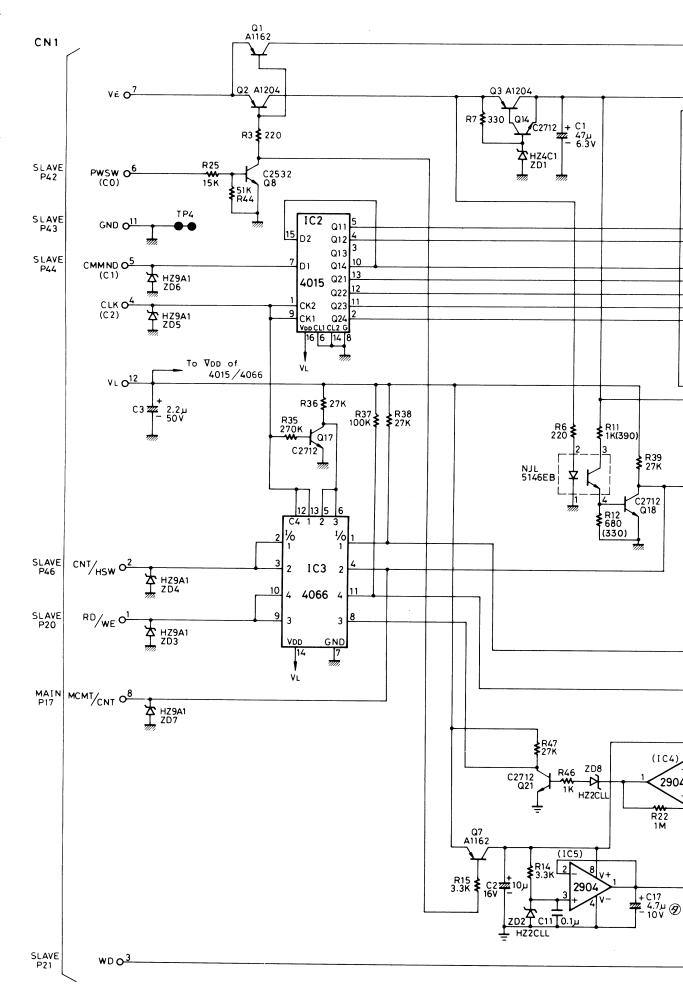

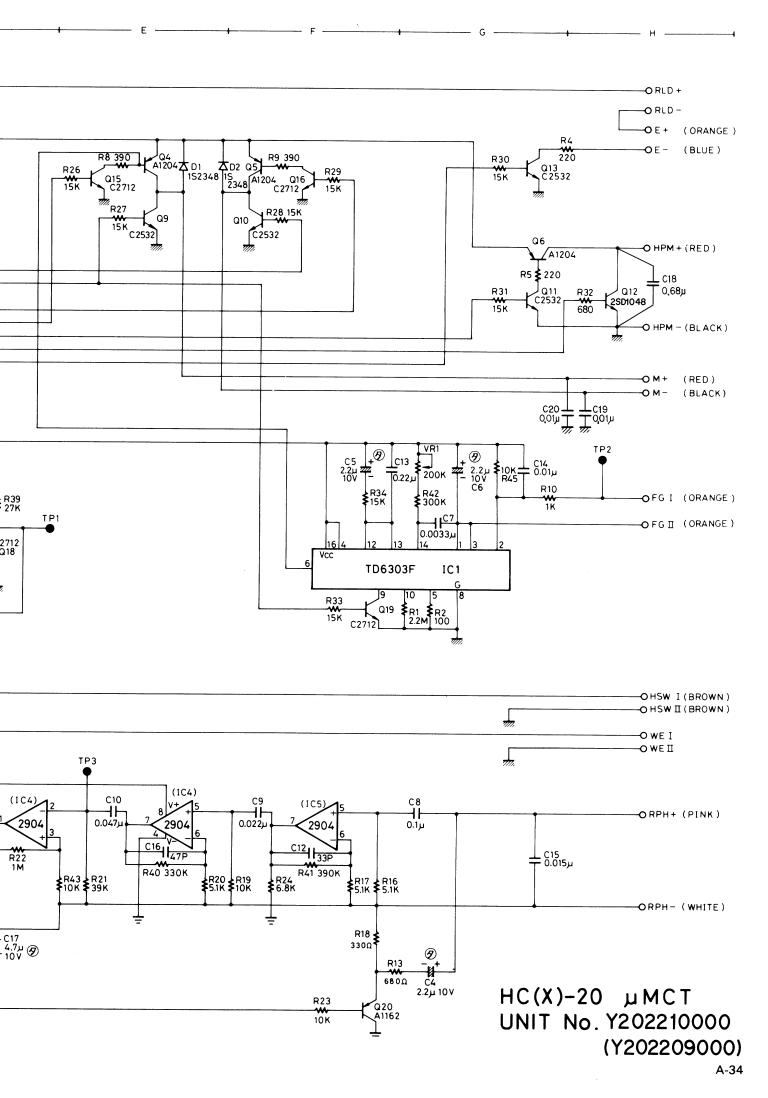

| TD6303F     | X440043030 | Motor control               | Microcassette IC1    |

|             |            |                             |                      |

|             |            |                             |                      |

|             |            |                             |                      |

A-6

2.2 ICs

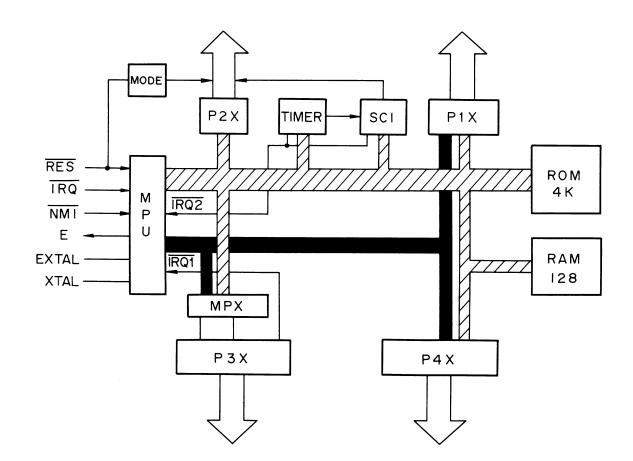

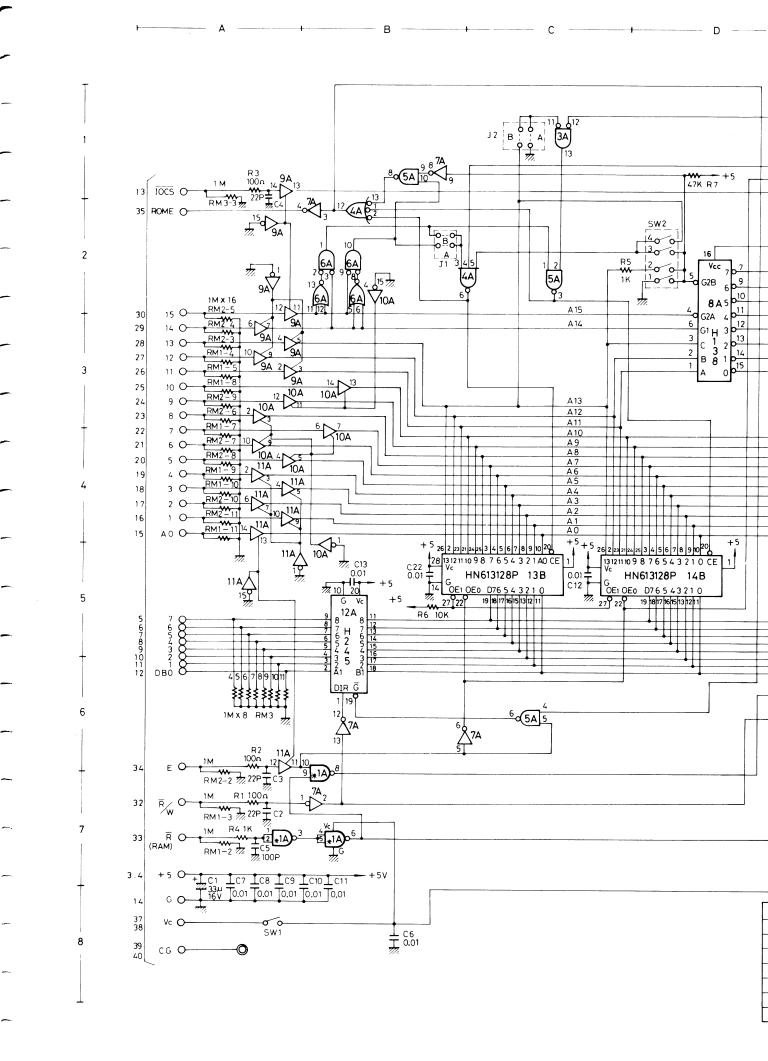

(1) 6301

The HX-20 employs a 2.4576 MHz crystal oscillator, whose output frequency is divided into one quarter by an internal circuit, i.e., 614.4 kHz (about every 1.63  $\mu$ sec.), which drives the HX-20.

The main CPU operates in the expanded multiplex mode, while the slave CPU operates in the single chip mode. Thus, the ports are used as shown below.

| Port   | Main CPU              | Slave CPU    |

|--------|-----------------------|--------------|

| Port 1 | Parallel I/O terminal | I/O terminal |

| Port 2 | Serial I/O terminal   | I/O terminal |

| Port 3 | Address/data terminal | I/O terminal |

| Port 4 | Address terminal      | I/O terminal |

Main CPU6301 (8G)

\_

| Pin No. | Port      | Direction | Mea                                  | ning                               |

|---------|-----------|-----------|--------------------------------------|------------------------------------|

| 1       | G         |           | GND                                  |                                    |

| 2       | X<br>TAL  | In        | Oscillator input 2.4576 MHz          |                                    |

| 3       | EX<br>TAL | In        | Oscillator input 2.4576 MHz          |                                    |

| 4       | NMI       | In        | Non-mask interrupt                   | Low: Interrupt                     |

| 5       | IRQ       | In        | I/O request                          | Low: On                            |

| 6       | RS        | In        | Reset signal                         |                                    |

| 7       | S.T.B.    | -         | Unused                               |                                    |

| 8       | 20        | In        | Bar code reader data line            |                                    |

| 9       | 21        | Out       | RS232C TX (transmitting data)        |                                    |

| 10      | 22        | Out       | Serial select                        | Low: Peripheral<br>High: Slave 63d |

| 11      | 23        | In .      | Slave 6301 serial (RX)               |                                    |

| 12      | 24        | Out       | Slave 6301 serial (TX)               |                                    |

| 13      | 10        | In        | Data set ready (DSR)                 | Low: On                            |

| 14      | 11        | In        | Clear to send (CTS)                  | Low: On                            |

| 15      | 12        | Out       | Slave CPU R/W control                |                                    |

| 16      | 13        | In        | External port interrupt              | Low: Interrupt                     |

| 17      | 14        | In        | Power abnormal<br>(PWA) (IRQ1)       | Low: Interrupt                     |

| 18      | 15        | In        | Keyboard interrupt<br>(IRQ1)         | Low: Interrupt                     |

| 19      | 16        | In        | Peripheral status<br>(Serial option) | Low: On                            |

| 20      | 17        | In        | Cartridge option flag                | Low: ROM<br>High: µCASSETTE        |

## Main CPU 6301 (8G)

| Pin No. | Port | Direction | Meaning          |

|---------|------|-----------|------------------|

| 21      | Vcc  |           | +5V              |

| 22      | A15  | Out       | Address bus      |

| 23      | A14  | Out       |                  |

| 24      | A13  | Out       |                  |

| 25      | A12  | Out       |                  |

| 26      | A11  | Out       |                  |

| 27      | A10  | Out       |                  |

| 28      | A9   | Out       |                  |

| 29      | A8   | Out       |                  |

| 30      | DA7  | In/Out    | Data address bus |

| 31      | DA6  | In/Out    |                  |

| 32      | DA5  | In/Out    |                  |

| 33      | DA4  | In/Out    |                  |

| 34      | DA3  | In/Out    |                  |

| 35      | DA2  | In/Out    |                  |

| 36      | DA1  | In/Out    |                  |

| 37      | DAO  | In/Out    |                  |

| 38      | R/W  | Out       | Read/write       |

| 39      | AS   | Out       | Address strobe   |

| 40      | E    | Out       | ENABLE           |

#### Slave CPU 6301 (6D)

|   | Pin No. | Port      | Direction |                                 | Meaning       | 3                                    |

|---|---------|-----------|-----------|---------------------------------|---------------|--------------------------------------|

|   | 1       | G         | _         | GND                             |               |                                      |

|   | 2       | X<br>TAL  | In        | Oscillator input 2              | 4576 (MHz)    |                                      |

|   | 3       | EX<br>TAL | In        | Oscillator input 2              | 4576 (MHz)    |                                      |

|   | 4       | NM1       | In        | Non-mask interrup               | t             | Low: ON                              |

|   | 5       | IRQ       | -         | Unused                          |               |                                      |

|   | 6       | R         | In        | Request signal                  |               |                                      |

|   | 7       | STB       | -         | Unused                          |               |                                      |

|   | 8       | 20        | In        | RS-232C (RX) receiving data     | Microcassette | LOW: READ DATA<br>HIGH: WRITE ENABLE |

|   | 9       | 21        | Out       | Microcassette<br>internal clock | Write data    |                                      |

|   | 10      | 22        | In        | Serial select                   |               | LOW: BRAKE<br>HIGH: NORMAL           |

|   | 11      | 23        | In        | Serial data (RX)                |               |                                      |

|   | 12      | 24        | Out       | Serial data (TX)                |               |                                      |

|   | 13      | 10        | Out       | Printer head 1                  |               | LOW: OFF<br><u>HIGH: ON</u>          |

|   | 14      | 11        | Out       | Printer head 2                  |               |                                      |

|   | 15      | 12        | Out       | Printer head 3                  |               |                                      |

|   | 16      | 13        | Out       | Printer head 4                  |               |                                      |

|   | 17      | 14        | Out       | Printer Motor                   |               | LOW: ON<br>HIGH: OFF                 |

|   | 18      | 15        | Out       | Speaker                         |               | LOW: OFF<br>HIGH: ON                 |

|   | 19      | 16        | In        | Printer reset pulse             |               |                                      |

|   | 20      | 17        | In        | Printer timing pulse            |               |                                      |

| L |         |           |           |                                 |               |                                      |

A-10

Slave CPU 6301 (6D)

| Pin No. | Port | Direction |                                       | Meaning                       |                                             |

|---------|------|-----------|---------------------------------------|-------------------------------|---------------------------------------------|

| 21      | Vcc  | _         | +5V                                   |                               |                                             |

| 22      | 47   | In        | Carrier detect                        |                               | Low: Carrier detected<br>High: Not detected |

| 23      | 46   | Out       | Rom cartridge<br>select               | Microcassette<br>Low: Counter | clock<br>High: Head switch                  |

| 24      | 45   | Out       | Cassette/RS-232C                      | select                        | Low: RS232-C<br>High: Microcassette         |

| 25      | 44   | Out       | ROM address count<br>clear            | ter                           | Clock                                       |

| 26      | 43   | Out       | ROM cartridge pow<br>Low: Off High: C |                               | Microcassette command                       |

| 27      | 42   |           | Clear shift<br>register               | Microca                       | ssette power switch<br>Low: Off High: On    |

| 28      | 41   | Out       | Port enable<br>always on              |                               | notor control<br>pen High: Brake            |

| 29      | 40   | In        | PLUG 2                                |                               |                                             |

| 30      | 37   | Out       | Program power on/                     | off                           | LOW: Off<br>High: On                        |

| 31      | 36   | Out       | RS-232 power on                       |                               | Low: Off<br>High: On                        |

| 32      | 35   | Out       | Bar code on/off                       |                               | Low: On<br>High: Off                        |

| 33      | 34   | Out       | Slave status flag                     |                               |                                             |

| 34      | 33   | Out       | External cassette w                   | rite data                     |                                             |

| 35      | 32   | In        | External cassette re                  | ad data                       |                                             |

| 36      | 31   | Out       | Request to send (R                    | rs)                           |                                             |

| 37      | 30   | Out       | External cassette re                  | emote on/off                  | Low: On<br>High: Off                        |

| 38      | _    | _         | Unused                                |                               |                                             |

| 39      | SC1  | _         | Unused                                |                               |                                             |

| 40      | -    | -         | Unused                                |                               |                                             |

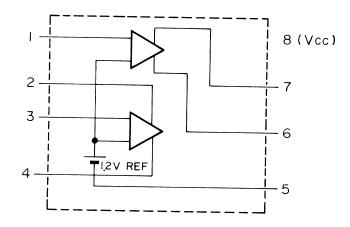

(2) MB 3761

(4) TD 62504

(Pin 9: Not used)

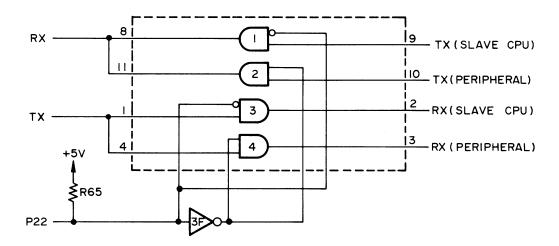

(5) 75188

(Pin 1: Vcc, 7 : GND)

(6) 75189

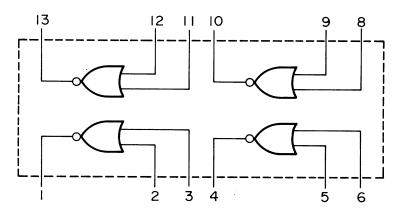

(Pin 7: GND, 14: Vcc)

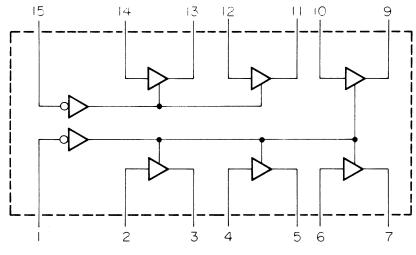

(7) TC 4016

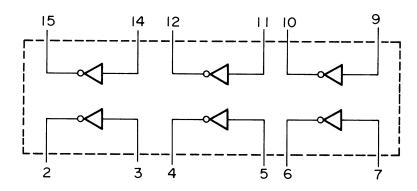

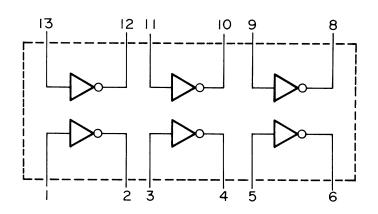

(8) 4049

(Pin 8: GND, 1: Vcc, 13/16 Unused)

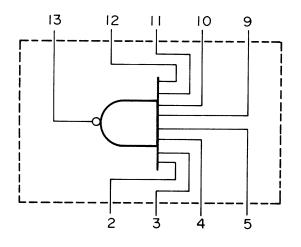

(9) 4068

(Pin 7: GND, 14: Vcc, 1/6/8: Unused)

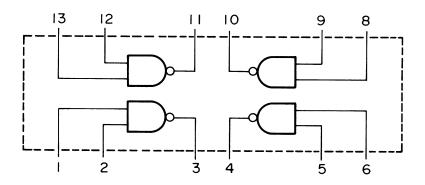

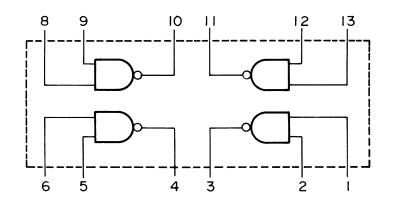

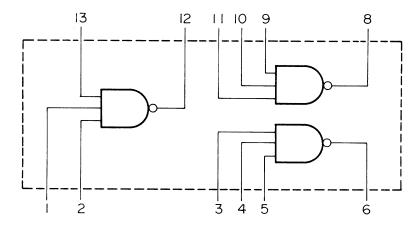

(10) 4093

#### (11) TC 4011BP

(Pin 7: Vss, 14: VDD)

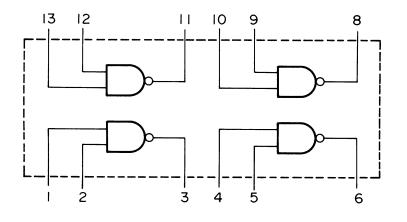

(12) 40H000P

(13) 40H002P

(Pin 7: GND, 14: VDD)

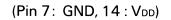

(14) 40H004P

(15) 40H010P

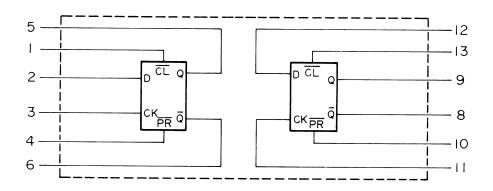

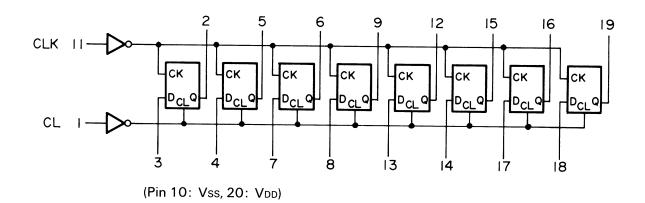

(16) 40H074P

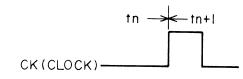

(D MODE) . . . . . . . . .  $\overline{\text{CL}}$  and  $\overline{\text{PR}}$  at high level

| tn | tn+l | Output |

|----|------|--------|

| D  | Q    | Q      |

| Н  | L    | н      |

| L  | Н    | L      |

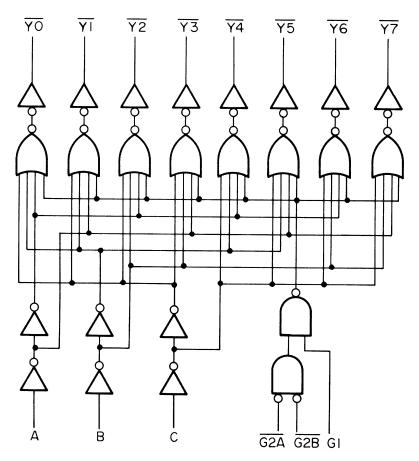

(17) 40H138

|    |      | In  | put |   |   |        |    |    |     |    |     |    |    |

|----|------|-----|-----|---|---|--------|----|----|-----|----|-----|----|----|

|    | Gate |     |     |   |   | Output |    |    |     |    |     |    |    |

| GI | G2A  | G2B | Α   | В | С | YO     | YI | Y2 | Y 3 | Y4 | Y 5 | Y6 | Y7 |

| L  |      | —   | -   |   | — | н      | н  | н  | н   | н  | н   | н  | н  |

| _  | н    | -   |     |   | — | н      | Н  | н  | Н   | Н  | н   | н  | н  |

| -  |      | Н   |     |   | - | н      | Н  | Н  | н   | Н  | н   | н  | н  |

| н  | L    | L   | L   | L | L | L      | Н  | Н  | Н   | Н  | н   | н  | н  |

| Н  | L    | L   | Н   | L | L | Н      | L  | Н  | Н   | н  | н   | н  | н  |

| н  | L    | L   | L   | Н | L | Н      | Н  | L  | Н   | Н  | Н   | н  | н  |

| Н  | L    | L   | Н   | Н | L | Н      | н  | Н  | L   | Н  | н   | Н  | н  |

| Н  | L    | L   | L   | L | Н | Н      | Н  | Н  | Н   | L  | Н   | н  | Н  |

| н  | L    | L   | Н   | L | Н | Н      | Н  | Н  | Н   | Н  | L   | н  | н  |

| Н  | L    | L   | L   | Н | Н | Н      | Н  | Н  | Н   | Н  | Н   | L  | н  |

| н  | L    | L   | Н   | Н | Н | Н      | Н  | Н  | Н   | Н  | Н   | Н  | L  |

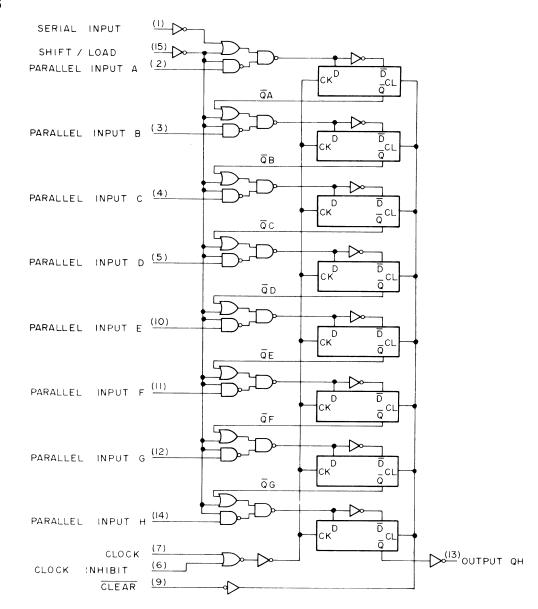

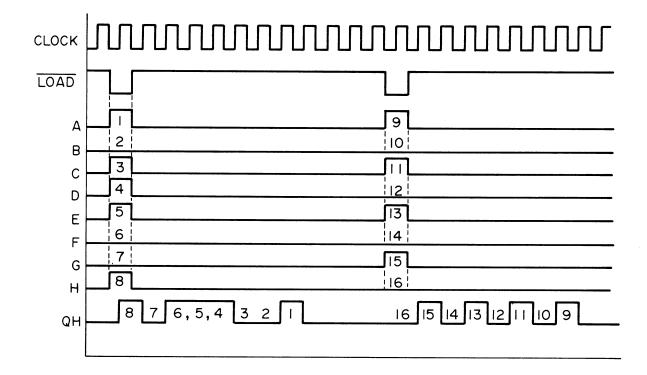

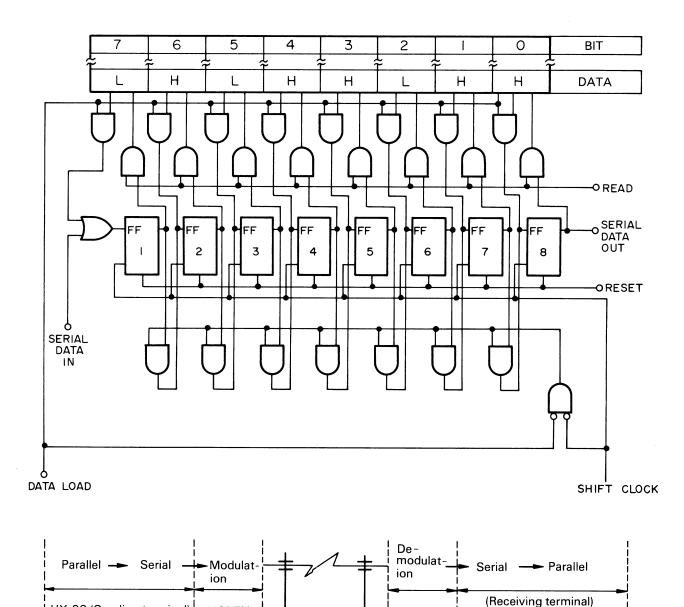

#### (18) 40H166

-

-

\_

\_

\_

\_

----

\_

\_

|       |        | INPUT   | 01    | UTPU'  | ΓЅ             | FUNCTION |                 |                  |                 |           |

|-------|--------|---------|-------|--------|----------------|----------|-----------------|------------------|-----------------|-----------|

| CLEAR | SHIFT/ | CLOCK   | CLOCK | SERIAL | PARALLEL INPUT |          | INTERNAL        |                  | 0.11            | FUNCTION  |

| CLEAR | LOAD   | INHIBIT | CLUCK | INPUT  | A              | Н        | Q A             | Q B              | QH              | MODE      |

| L     | *      | *       | *     | *      | *              | *        | L               | L                | L               | Clear     |

| Н     | Н      | L       | Î     | L      | *              | *        | L               | Q <sub>An</sub>  | QGn             | S1:6      |

| Н     | Н      | L       | Ť     | Н      | *              | *        | Н               | Q <sub>An</sub>  | QGn             | Shift     |

| Н     | L      | L       | ſ     | *      | L              | L        | L               | P <sub>INB</sub> | L               |           |

| Н     | L      | L       | Ť     | *      | L              | Н        | L               | P <sub>INB</sub> | Н               | Parallel  |

| Н     | L      | L       | Î     | *      | Н              | L        | Н               | P <sub>inb</sub> | L               | Load      |

| Н     | L      | L       | Ť     | *      | Н              | Н        | Н               | P <sub>INB</sub> | Н               |           |

| Н     | *      | Н       | *     | *      | *              | *        | Q <sub>AO</sub> | Q <sub>B0</sub>  | Qно             | Hold      |

| Н     | *      | *       | ↓     | *      | *              | *        | Q <sub>AO</sub> | $Q_{BO}$         | Q <sub>HO</sub> | No change |

A-18

(19) 40H166

H273

(20) 40H367

H373

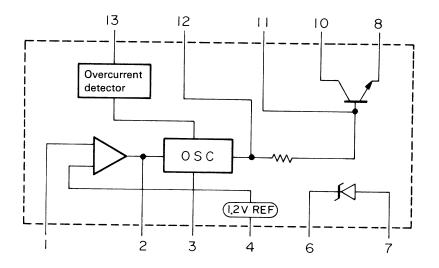

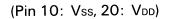

(21) TD6303F

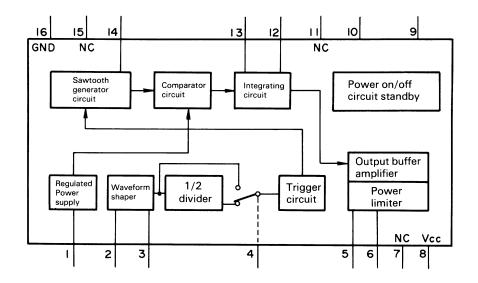

## 3. Serial – Parallel Conversion

HX-20 (Sending terminal)

MODEM

r

The HX-20 converts data program-wise. The concept of serial  $\leftrightarrow$  parallel conversion using the hardware shown below is explained.

Data conversion from serial to parallel and vice versa is necessary for reducing the number of communication lines in data transfer.

**Communication line**

MODEM

Serial-parallel conversion performed by the above circuit is briefly explained on the next page.

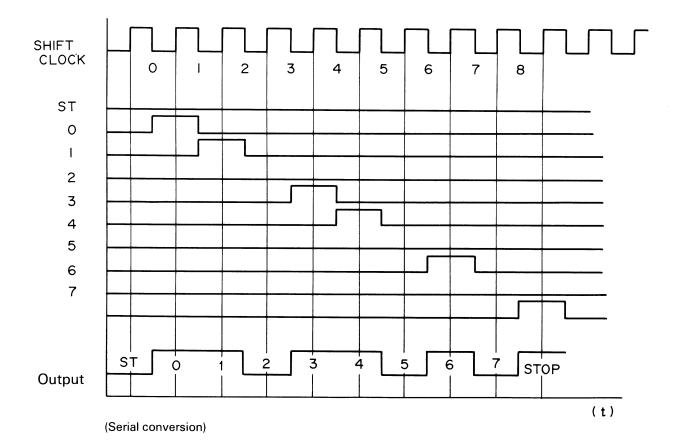

#### 3.1 Parallel to Serial Conversion (Add start and stop bits.)

After the flip-flop circuit is reset by a reset signal, parallel data is read into FF '1' to FF '8' by a data load signal.

Then, the data is shifted bit by bit at the timing of NOT DATA LOAD and SHIFT CLOCK, and these bits are output to SERIAL DATA OUT. In performing this operation, it is necessary to add a start bit and a stop bit to the data.

#### 3.2 Serial to Parallel Conversion

After resetting the flip-flop with a reset signal, the serial data bits coming from SERIAL DATA IN are set into FF '1', and are shifted bit by bit at the SHIFT CLOCK timing.

After shifting 1 byte of data bits, the bits are read out to the parallel data line by a read signal. In this conversion operation, the start bit and stop bit are separated from the data.

# 4. Main Circuit Signals

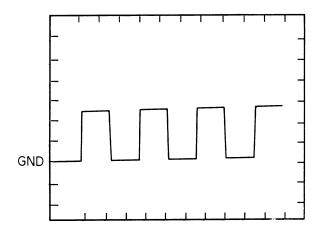

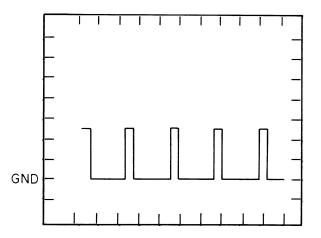

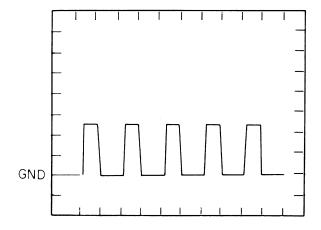

### 4.1 Enable Signal (E)

| POINT   | IC 8G PIN 40      |

|---------|-------------------|

| VOLTAGE | 2.0V DC/DIV       |

| SWEEP   | 0.5 <i>μ</i> sec. |

A system clock with a period of 1.6  $\mu$ sec \*A pulse waveform is always output if power is on.

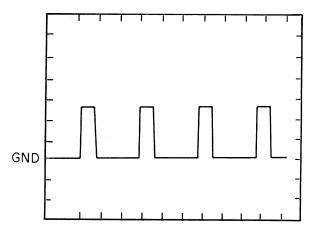

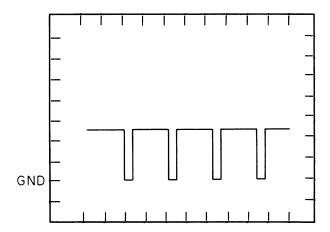

## 4.2 Address Strobe Signal (AS)

| POINT IC | 8G PIN39          |

|----------|-------------------|

| VOLTAGE  | 2.0V DC/DIV       |

| SWEEP    | 0.5 <i>μ</i> sec. |

This signal is output every 1.6  $\mu$ sec.

\*A pulse waveform is always output if power is on.

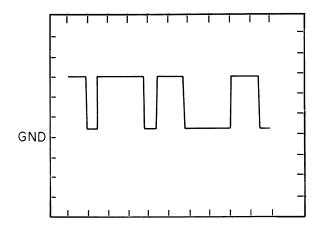

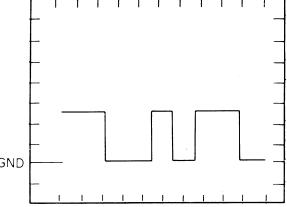

#### 4.3 Address/Data Bus Signal

| POINT   | IC 8G PIN37       |

|---------|-------------------|

| VOLTAGE | 2.0V DC/DIV       |

| SWEEP   | 1.0 <i>μ</i> sec. |

Address/data buses are not constant depending on the program command and data being executed.

\* Normally high level

## 4.4 LCD Chip Select Signal (CS)

GND

## 4.5 LCD Shift Clock Signal (SCK)

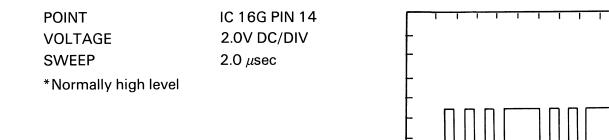

| POINT                | IC 11H PIN2       |

|----------------------|-------------------|

| VOLTAGE              | 2.0V DC/DIV       |

| SWEEP                | 2.0 <i>μ</i> sec. |

| *Normally high level |                   |

## 4.6 Clock Pulse for Clock

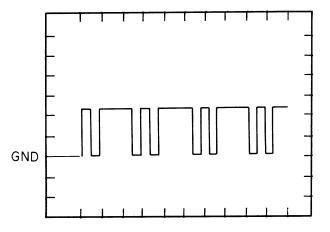

| POINT   | IC 6G PIN2       |

|---------|------------------|

| VOLTAGE | 2.0V DC/DIV      |

| SWEEP   | 10 <i>µ</i> sec. |

\*Normally a pulse waveform

# 4.7 KSC Signal

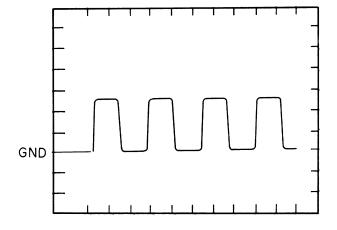

| POINT               | IC 5G PIN5  |

|---------------------|-------------|

| VOLTAGE             | 2.0V DC/DIV |

| SWEEP               | 0.2 msec    |

| *Normally low level |             |

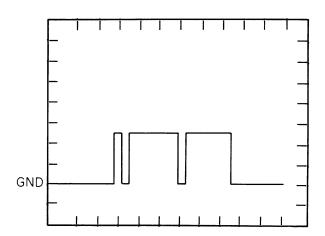

# 4.8 Key Input Control Signal

| POINT               | IC 6C PIN13   |

|---------------------|---------------|

| VOLTAGE             | 2.0V DC/DIV   |

| SWEEP               | 50 $\mu$ sec. |

| *Normally low level |               |

# 4.9 KB REQUEST Signal

| POINT                | IC 8G PIN18      |

|----------------------|------------------|

| VOLTAGE              | 2.0V DC/DIV      |

| SWEEP                | 50 <i>µ</i> sec. |

| *Normally high level |                  |

## 4.10 Cassette Write Waveform Slave Output

| POINT<br>VOLTAGE<br>SWEEP                                   | IC 6D PIN 33<br>2.0V DC/DIV<br>0.5 msec |     |  |

|-------------------------------------------------------------|-----------------------------------------|-----|--|

| Bit on where pulse<br>pulse is narrow<br>*Normally low leve | e is wide; bit off where                |     |  |

|                                                             |                                         | GND |  |

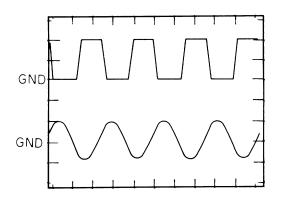

#### 4.11 Cassette Read Waveform

| POINT   | IC 8D PIN7  |

|---------|-------------|

| VOLTAGE | 2.0V AC/DIV |

| SWEEP   | 0.5 msec.   |

All bits are off. When bit is on, pulse width is twice as large.

\*Normally high level

#### 4.12 Cassette Read Waveform

| POINT   | IC 8D PIN6  |

|---------|-------------|

| VOLTAGE | 2.0V DC/DIV |

| SWEEP   | 0.5 msec.   |

This is a shaped version of the above input to IC 8D Pin 7.

\*Normally low level

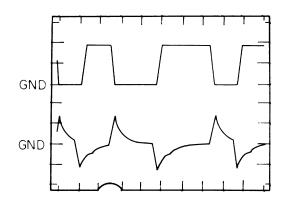

#### 4.13 Microcassette Read Waveform

|         | CH1         | CH2         |

|---------|-------------|-------------|

| POINT   | IC4 PIN1    | IC4 PIN2    |

| VOLTAGE | 2.0V DC/DIV | 0.5V DC/DIV |

| SWEEP   | 0.1 msec    | 0.1 msec    |

#### 4.14 Microcassette Read Waveform

|         | CH1         | CH2         |

|---------|-------------|-------------|

| POINT   | IC4 PIN1    | IC4 PIN2    |

| VOLTAGE | 2.0V DC/DIV | 2.0V DC/DIV |

| SWEEP   | 0.1 msec.   | 0.1 msec.   |

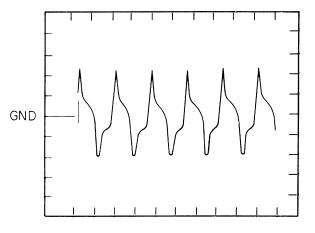

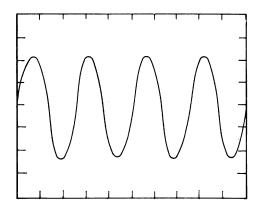

## 4.15 Tachogenerator Output

| POINT   | R16         |

|---------|-------------|

| VOLTAGE | 0.2V AC/DIV |

| SWEEP   | 1.0 msec.   |

This signal has a period of 400 Hz. In case of no speed control (REW/FF), the period increases to more than 400 Hz and the waveform to about 1.5 Vp-p.

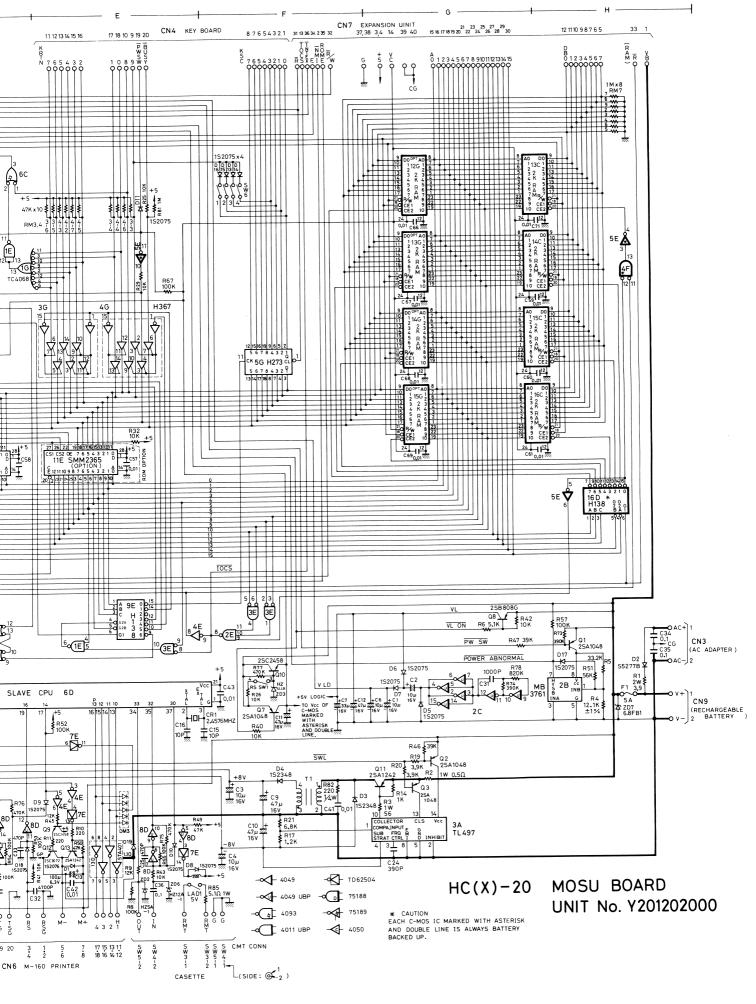

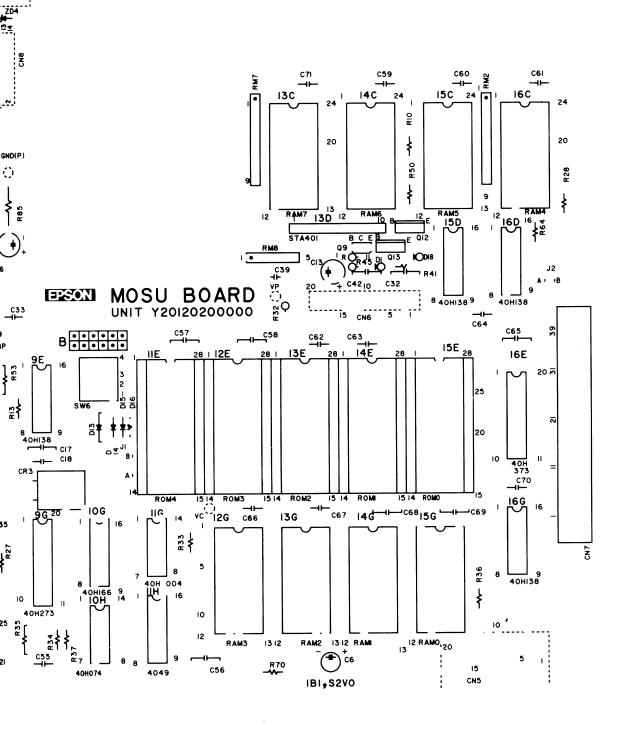

(MOSU BOARD COMPORNENT SIDE V

OMPORNENT SIDE VIEW)

Ε

(MOSU BOARD REAR SI

**BOARD REAR SIDE VIEW)**

-

Е

F

G

н -

A-32

8

Е

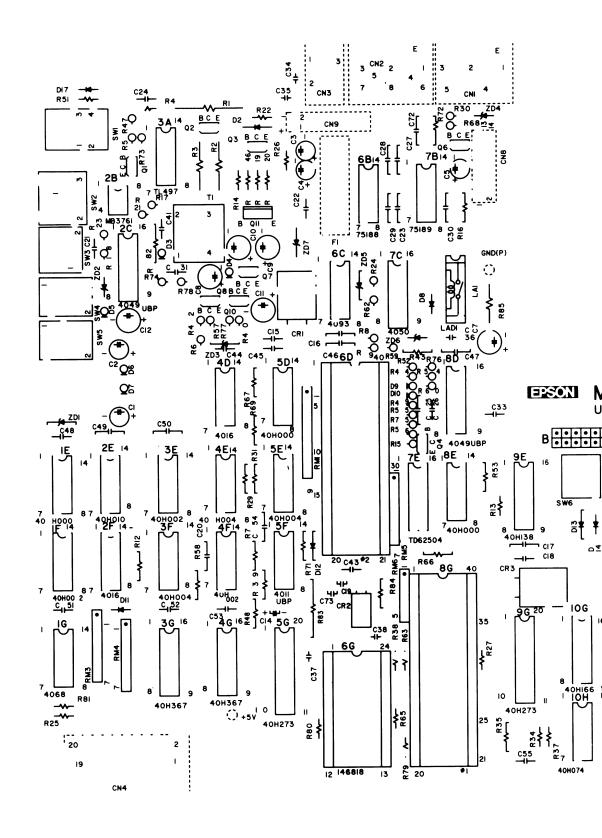

HC(X)-20 ROM CAT UNIT No. Y202201000

ļ.....

н

G

| USAGE LOCATION | IC TYPE  | USAGE LOCATION | IC TYPE      |

|----------------|----------|----------------|--------------|

| 10             | M51342P  | 5C             | 40H245P      |

| 2 C            | M506847P | 5 D            | 2016P        |

| 3B 8A          | 4049UBP  | 6 A            | 40H008P      |

| 3C             | 40H244P  | 6 B            | 40H373P      |

| 3D 5B          | 40H004P  | 6 C            | 40H367P      |

| 4A             | 40H000P  | 7 A            | 74 L S 9 2 P |

| 4B             | 40H074P  | 7 B            | 63011CA      |

| 4C             | D2732D   | 9 A            | SN75189      |

| 4D             | 40H193P  | 10 A           | SN75188      |

| 5A             | 74LS32   |                |              |

HC(X) - 20 TVA BOARD UNIT NO. Y202203200

G

| IC TYPE | USAGE LOCATION |

|---------|----------------|

| 40 H000 | 1A 5A          |

| 40 H002 | 3A 6A          |

| 40H004  | 7A             |

| 40H010  | 4A             |

| 40H138  | 2A 8A          |

| 40H367  | 9A 10A 11A     |

| 40H245  | 12A            |

#### \* CAUTION

IC'IA' MARKED WITH ASTARISK AND DOUBLE LINE IS ALWAYS BATTERY BACKED UP. HC(X)-20 EXP BOARD UNIT No. Y202204000

EPSON CORPORATION

**BUSINESS & INDUSTRIAL INSTRUMENT DIVISION**

#### EPSON OVERSEAS MARKETING LOCATIONS

EPSON AMERICA, INC. (L.A.) 3415 Kashiwa Street. Torrance, CA. 90505 U.S.A. Phone: (213) 539-9140 Telex: 182412

#### EPSON DEUTSCHLAND GmbH

Am Seestern 24 4000 Düsseldorf 11, F.R. Germany Phone: 0211-5961001 Telex: 8584786

#### EPSON U.K. LTD.

Dorland House, 1F 388 High Road, Wembley London Phone: (01) 900-0466/9 Telex: 8814169

#### EPSON CORPORATION SINGAPORE REPRESENTATIVE OFFICE

Suite 813, 8th Floor, World Trade Centre No1, Maritime Square Telok Blangah Road, Singapore 0409 Phone: 2786071/2 Telex: RS39536